Poiché il chip RV1126 è stato interrotto, consigliamo IPC2188 come soluzione sostitutiva.

Fare clic sul collegamento in basso per ulteriori dettagli: Ulteriori informazioni su IPC2188

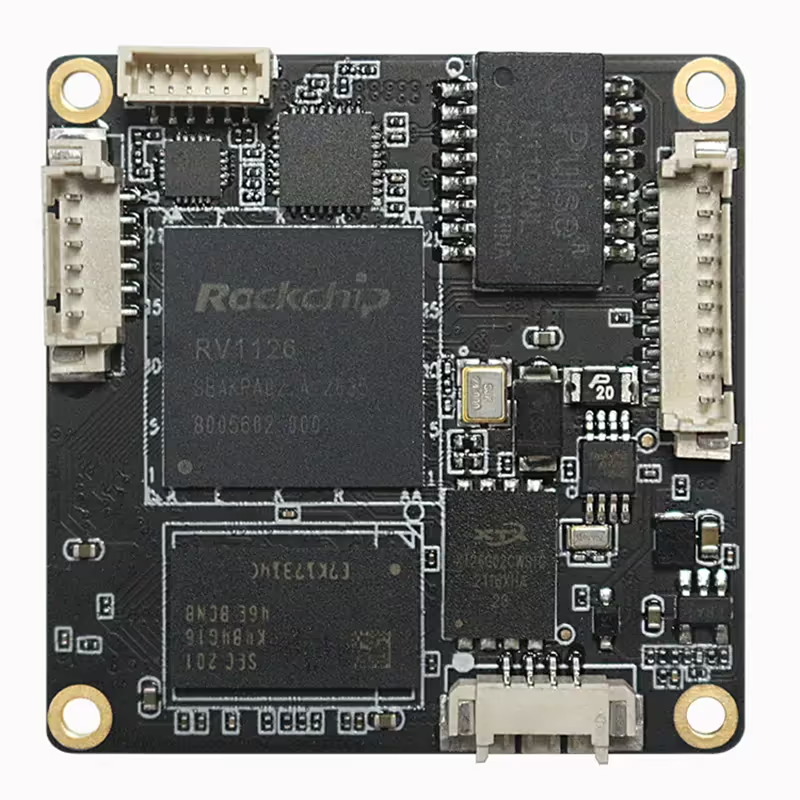

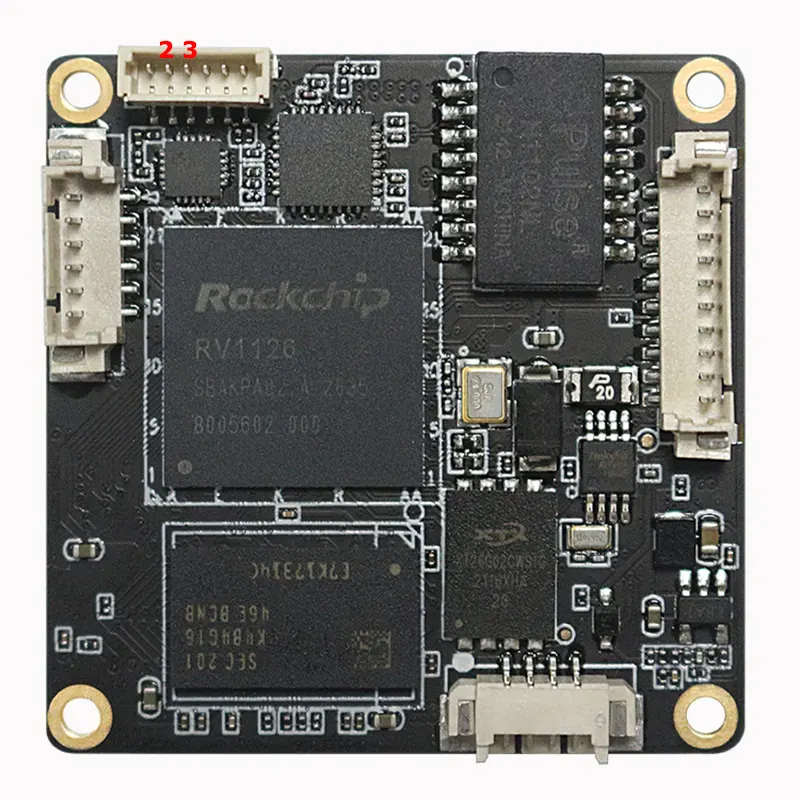

Rockchip RV1126 Development Evaluation Board Core Board IPC AI SDK Software Development Kit

Sommario

Galleria

Applicazioni del prodotto

IPC intelligente, Macchina del pannello di riconoscimento facciale, Fotocamera per l'acquisizione del viso, Campanello video, Nessuna rete, e Nessuna fotocamera di alimentazione, Palmare espresso, navigazione GPS, Interfaccia uomo-macchina, Apparecchiature di monitoraggio, Pod per droni, Sistema di videoconferenza, eccetera.

Vuoi lavorare con il modulo della fotocamera con obiettivo Sony IMX415?

Scarica l'SDK

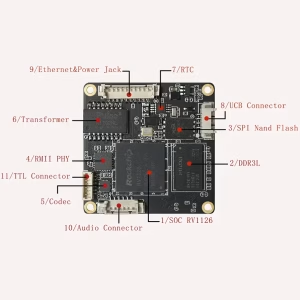

Specifica vista frontale

1. SOC RV1126, Pin to Pin compatibile con RV1109;

|

Pin1 |

VCC5V0_OTG |

|

Pin2 |

OTG_DM |

|

Pin3 |

OTG_DP |

|

pin4 |

GND |

9.Ethernet&Jack di alimentazione

|

Pin1 |

TX+ |

Pin6 |

RX- |

|

Pin2 |

TX- |

Pin7 |

POE78 |

|

Pin3 |

RX+ |

Pin8 |

POE78 |

|

pin4 |

POE45 |

Pin9 |

GND |

|

Pin5 |

POE45 |

Pin10 |

VCC12V_DCIN |

10. Connettore audio

|

Pin1 |

LED1/PHYAD1 |

|

Pin2 |

LED0 / PHYAD0 |

|

Pin3 |

RIPRISTINA |

|

pin4 |

MICP |

|

Pin5 |

GND |

|

Pin6 |

LINE_OUT |

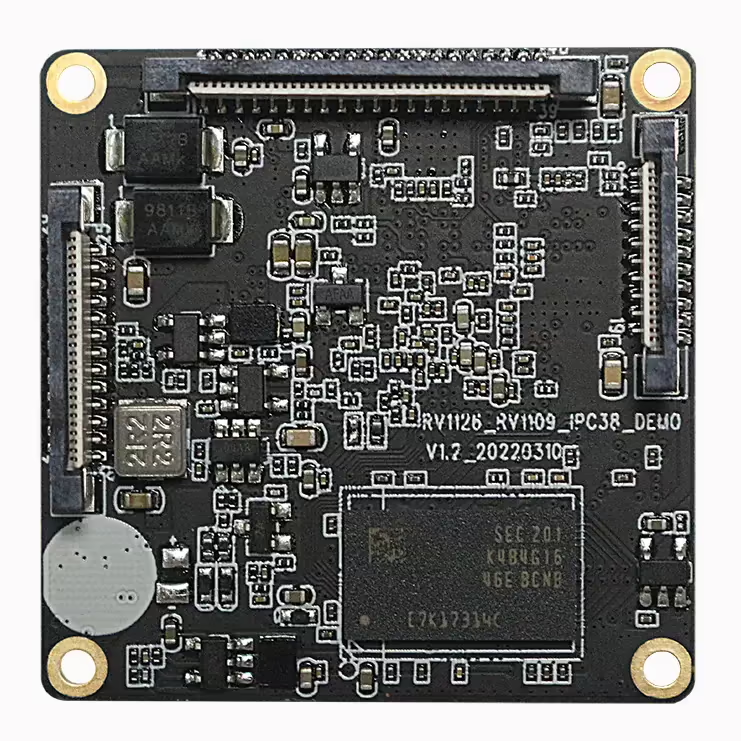

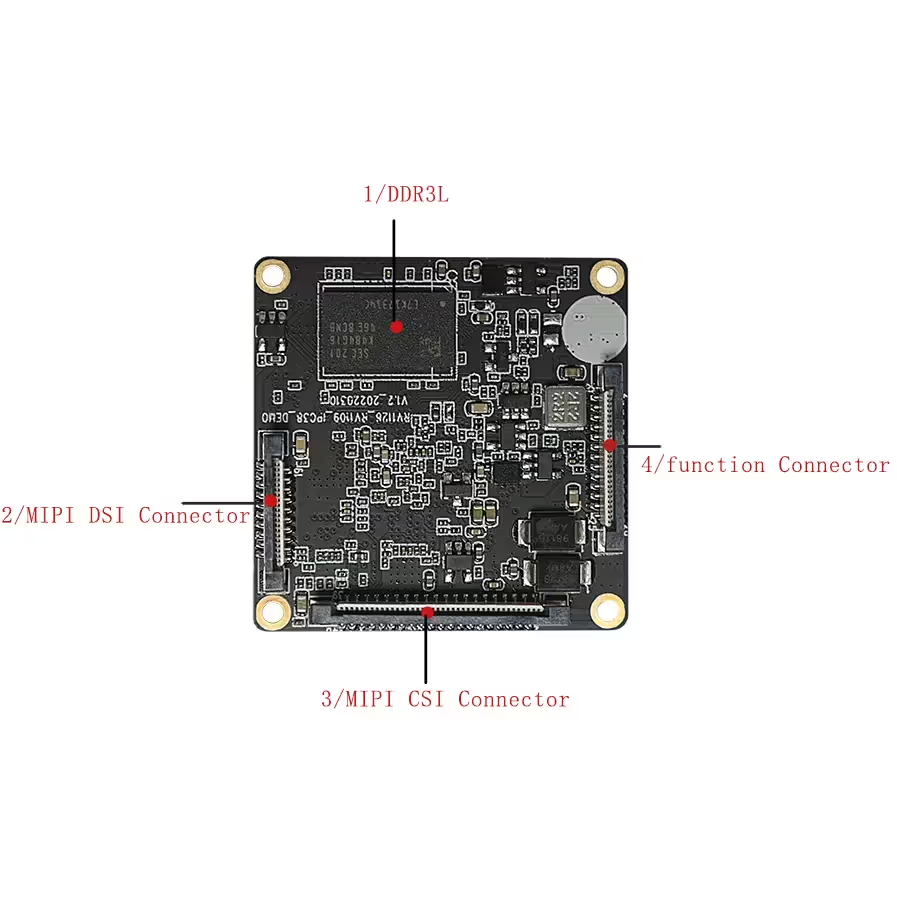

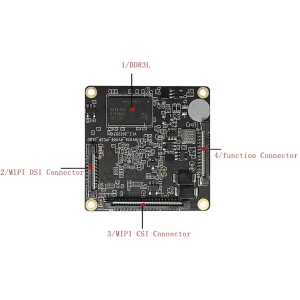

Specifiche della vista posteriore

1.DDR3L (Samsung K4B4G1646E BCNB)

Una DDR3 da 4 Gbit è collegata alla parte anteriore e posteriore dell'intera scheda, con un totale di 8G bit;

2.Connettore MIPI DSI

|

Pin1 |

IRQ |

Pin11 |

MIPI_DSI_D3N |

|

Pin2 |

PWR_IT |

Pin12 |

MIPI_DSI_D3P |

|

Pin3 |

RST |

Pin13 |

MIPI_DSI_D0N |

|

pin4 |

I2C3_SDA |

Pin14 |

MIPI_DSI_D0P |

|

Pin5 |

I2C3_SCL |

Pin15 |

GND |

|

Pin6 |

GND |

Pin16 |

MIPI_DSI_CLKN |

|

Pin7 |

MIPI_DSI_D2P |

Pin17 |

MIPI_DSI_CLKP |

|

Pin8 |

MIPI_DSI_D2N |

Pin18 |

GND |

|

Pin9 |

MIPI_DSI_D1P |

Pin19 |

VCC_12V |

|

Pin10 |

MIPI_DSI_D1N |

Pin20 |

VCC_12V |

3.Connettore CSI MIPI

|

Pin1 |

VCC3V3_SYS |

Pin21 |

MIPI_CSI_RX0_D1N |

|

Pin2 |

VCC3V3_SYS |

Pin22 |

MIPI_CSI_RX0_D0P |

|

Pin3 |

SPI0_CLK |

Pin23 |

MIPI_CSI_RX0_D0N |

|

pin4 |

LED_PWM |

Pin24 |

GND |

|

Pin5 |

SPI0_CS0N |

Pin25 |

MIPI_CSI_CLK0 |

|

Pin6 |

SPI0_MISO |

Pin26 |

GND |

|

Pin7 |

SPI0_MOSI |

Pin27 |

PWM8 |

|

Pin8 |

I2C1_SDA |

Pin28 |

IRC_AIN |

|

Pin9 |

I2C1_SCL |

Pin29 |

PWM11 |

|

Pin10 |

MIPI_RX0_PDN |

Pin30 |

PWM9 |

|

Pin11 |

MIPI_RX0_RST |

Pin31 |

IRC_BIN |

|

Pin12 |

GND |

Pin32 |

ZOOM_IT |

|

Pin13 |

MIPI_CSI_RX0_CLKP |

Pin33 |

PWM10 |

|

Pin14 |

MIPI_CSI_RX0_CLKN |

Pin34 |

P-IRIS_IT |

|

Pin15 |

GND |

Pin35 |

FUOCO_IT |

|

Pin16 |

MIPI_CSI_RX0_D2P |

Pin36 |

ADC_IN |

|

Pin17 |

MIPI_CSI_RX0_D2N |

Pin37 |

GND |

|

Pin18 |

MIPI_CSI_RX0_D3P |

Pin38 |

VCC_1V8 |

|

Pin19 |

MIPI_CSI_RX0_D3N |

Pin39 |

VCC_12V |

|

Pin20 |

MIPI_CSI_RX0_D1P |

Pin40 |

VCC_12V |

4.Connettore di funzione

|

Pin1 |

HOST_DM |

Pin14 |

SDMMC0_D0 |

|

Pin2 |

HOST_DP |

Pin15 |

SDMMC0_CLK |

|

Pin3 |

GND |

Pin16 |

SDMMC0_D3 |

|

pin4 |

GND |

Pin17 |

RS485_CTL |

|

Pin5 |

ALLARME_IN |

Pin18 |

UART3_RX_485 |

|

Pin6 |

SDMMC0_DET |

Pin19 |

UART3_TX_485 |

|

Pin7 |

ALLARME_USCITA |

Pin20 |

GND |

|

Pin8 |

SDMMC0_PWREN |

Pin21 |

VCC_12V |

|

Pin9 |

SDMMC0_D2 |

Pin22 |

VCC_12V |

|

Pin10 |

USB_PWREN |

Pin23 |

POE45 |

|

Pin11 |

SDMMC0_CMD |

Pin24 |

POE78 |

|

Pin12 |

GND |

Pin25 |

POE36 |

|

Pin13 |

SDMMC0_D1 |

Pin26 |

POE12 |

Domande frequenti

- L'indirizzo IP predefinito della telecamera è 192.168.31.88.

- se colleghi il nostro campione tramite cavo di rete al tuo computer, puoi usare questo 169.254.95.254 per modificare il parametro.

Utente: amministratore

Parola d'ordine: amministratore

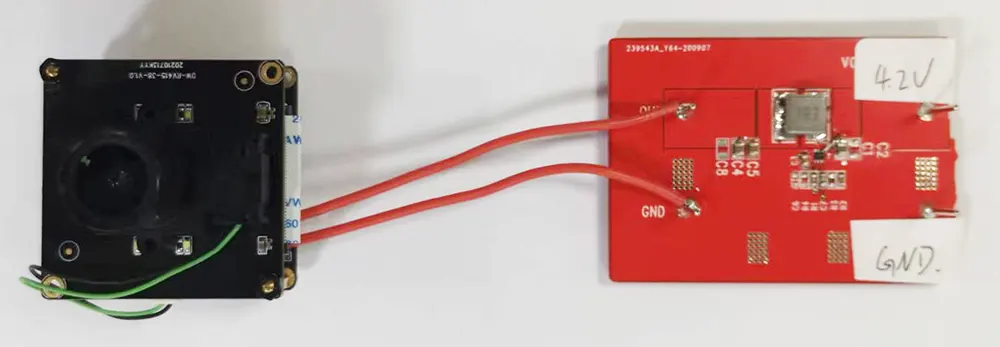

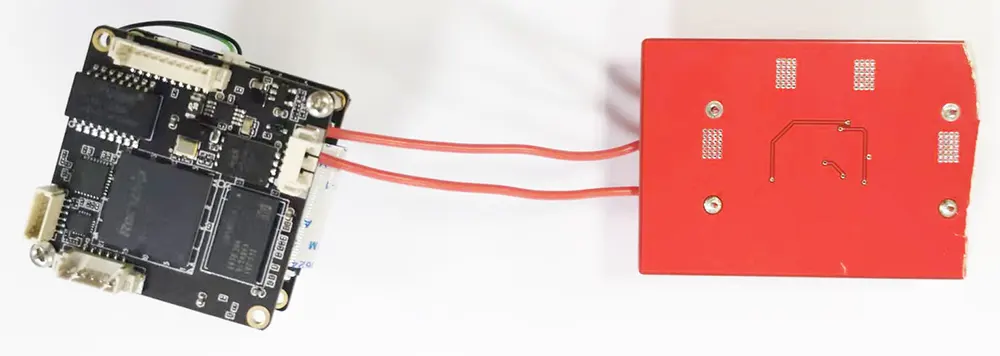

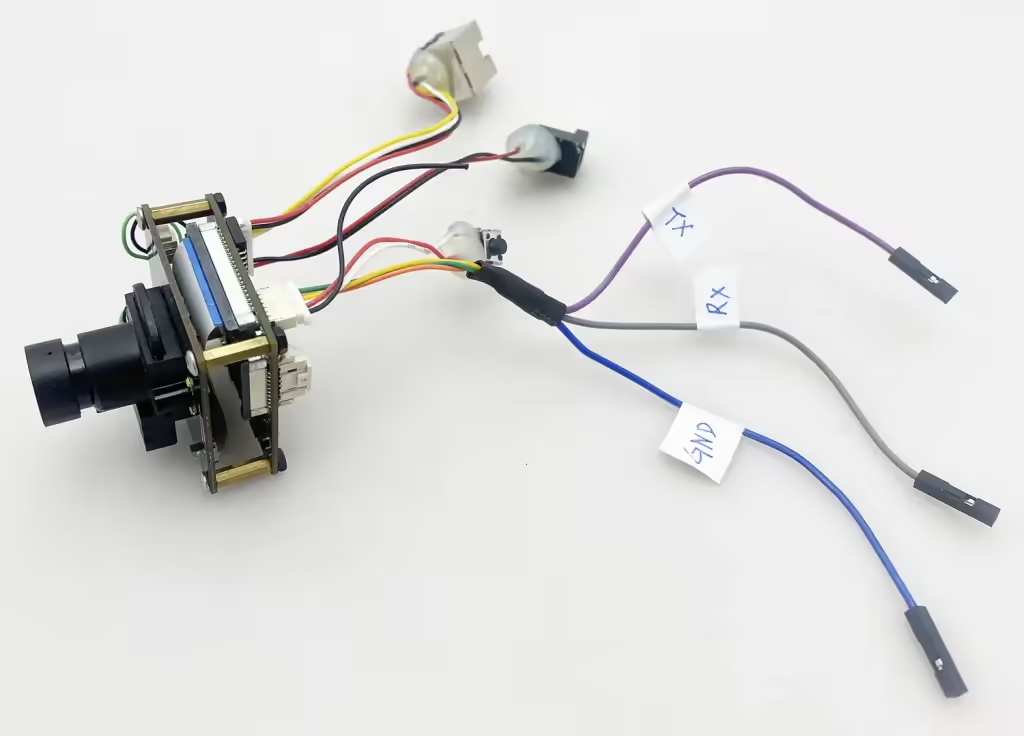

Si prega di verificare l'immagine qui sotto, Solo a breve un breve collegamento P2 e P3 e attiverà l'inizio. quindi puoi allentare la connessione.

sì, modificheremo in base alle vostre esigenze.

Hai bisogno 4.2 volt, dobbiamo sostituire il circuito integrato di alimentazione, ma i pin e i circuiti periferici dei due circuiti integrati di potenza sono diversi. I nostri ingegneri hanno provato molti metodi ma non possono modificare direttamente la scheda originale, quindi possiamo usarlo solo temporaneamente. Sul tabellone rosso, un IC di alimentazione è collegato per soddisfare le tue esigenze.

https://youtube.be/toh4bY1kTuw

La dimensione della scheda pcba è 38x38mm

Il diametro dei quattro fori è di 2 mm

La distanza tra i due fori è di 34 mm

utente: radice

parola d'ordine: rockchip

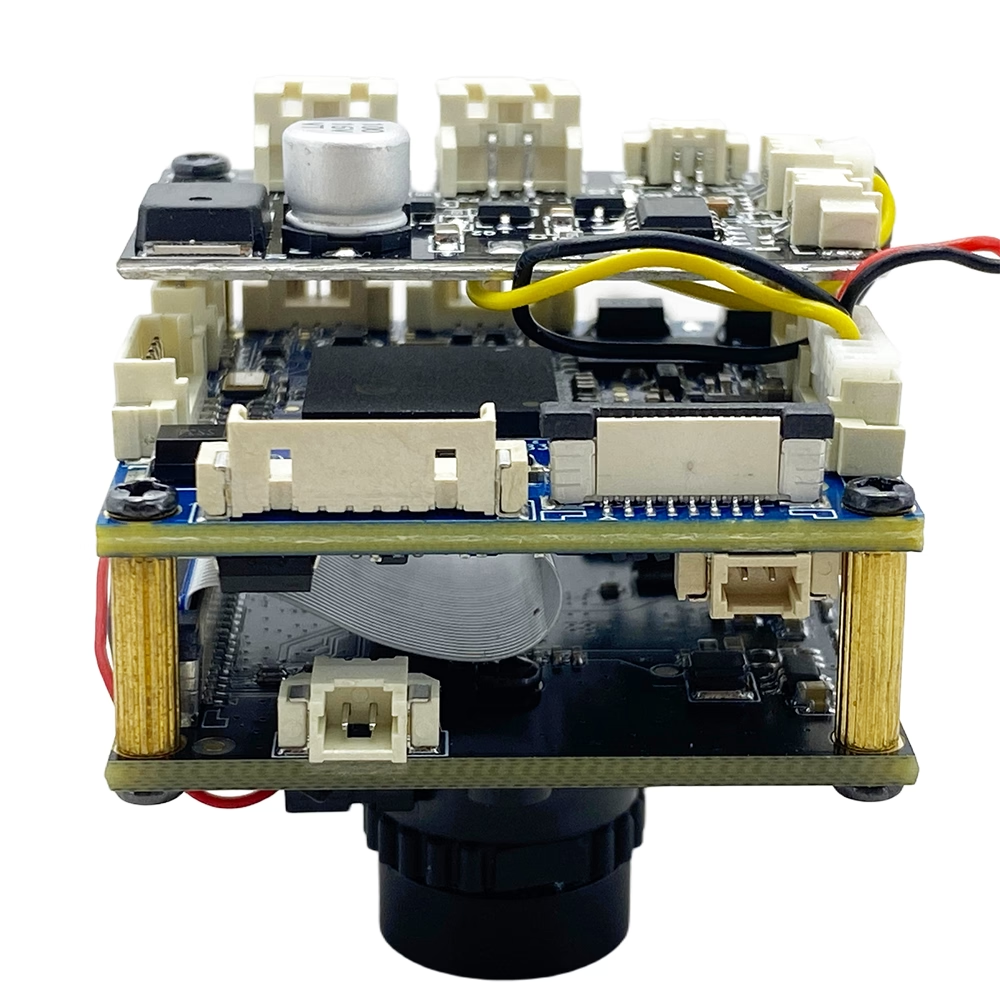

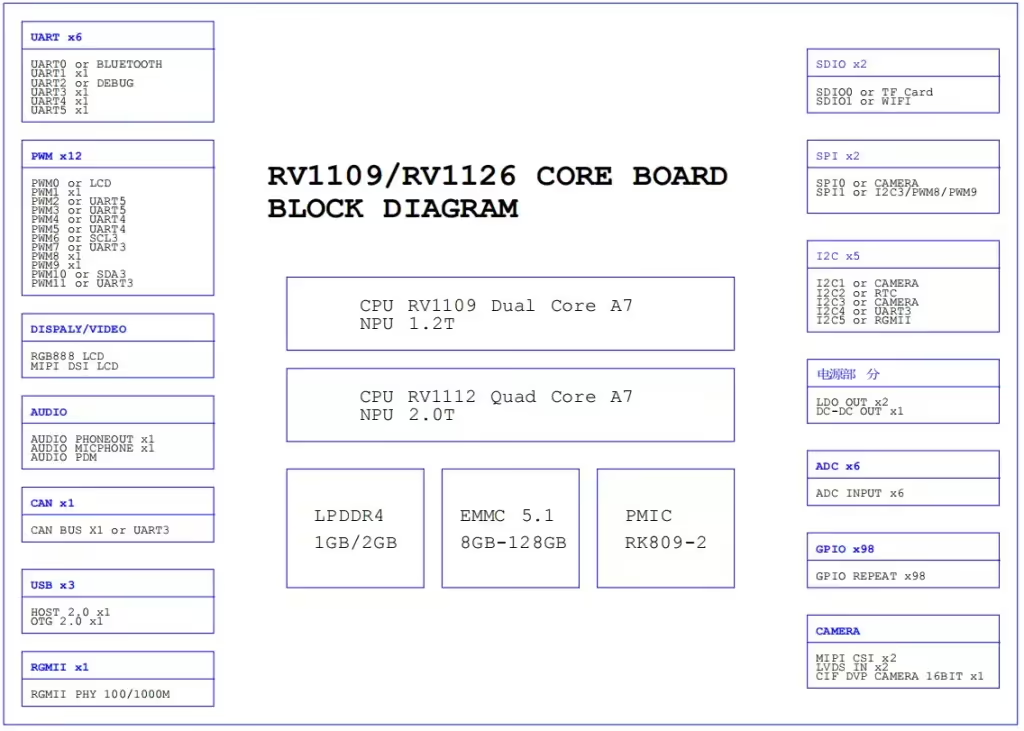

Requisiti hardware

1. Modulo telecamera Sony IMX415 (Modulo telecamera con interfaccia MIP)

2. Cavo a nastro MiPi (cavo per collegare la telecamera con SBC PCB)

3. Telecamera principale RV1126 verso

4. Cablaggio (Cablaggio con USB POE, Energia, e connettore audio RCA)

5. Scheda POE B per SBC (Scheda adattatore POE per PCB SBC)

6. Adattatore di alimentazione (Fonte di alimentazione CC per unità fotocamera)

7. Programmazione USB / cavo di debug (OTe) (USB separata, Cavo di tipo OTG per programmare ed eseguire il debug di SBC)

8. GUIDATO / Schede IR (Scheda IR e LED per il montaggio della telecamera)

9. MIC

10. Samsung eMMC con memoria basata su SLC/MLC

11. Ram Samsung

12. Ethernet Realtek: con supporto PoE

13. Batteria dell'RTC

sì, siamo lieti di sviluppare una nuova funzionalità per soddisfare la tua richiesta.

sì, la nostra scheda di sviluppo RV1126 ha un supporto aggiuntivo per il lettore di schede TF.

ok. Ti invierò via e-mail.

Risposta: L'ingegnere ha risposto che il suo strumento di sviluppo Rockchip RV1126 è solo per Windows.

Domanda: Avremo accesso root? Se siamo root possiamo installare qualsiasi nostro programma (incl. Linux)

Risposta: sì.

Domanda: Posso chiederti di collegarti ai repository per scaricare l'SDK, (strumenti di sviluppo)?

Risposta: sì, RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=condivisione

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=condivisione

Domanda: Abbiamo bisogno di un composito (CVBS) video sul modulo Rockchip RV1126. Puoi sostenerlo?? Aggiungi solo DSI al chip convertitore video analogico.

Risposta: Hai bisogno della scheda di sviluppo RV1126 per supportare un composito (CVBS) ingresso per la normale telecamera CVBS?

Se si, si prega di controllare il link sottostante, lo sviluppiamo per un altro cliente.

RV1126 personalizzato per telecamera USB web o CVBS.

Possiamo anche sviluppare l'altra funzione se ne hai bisogno.

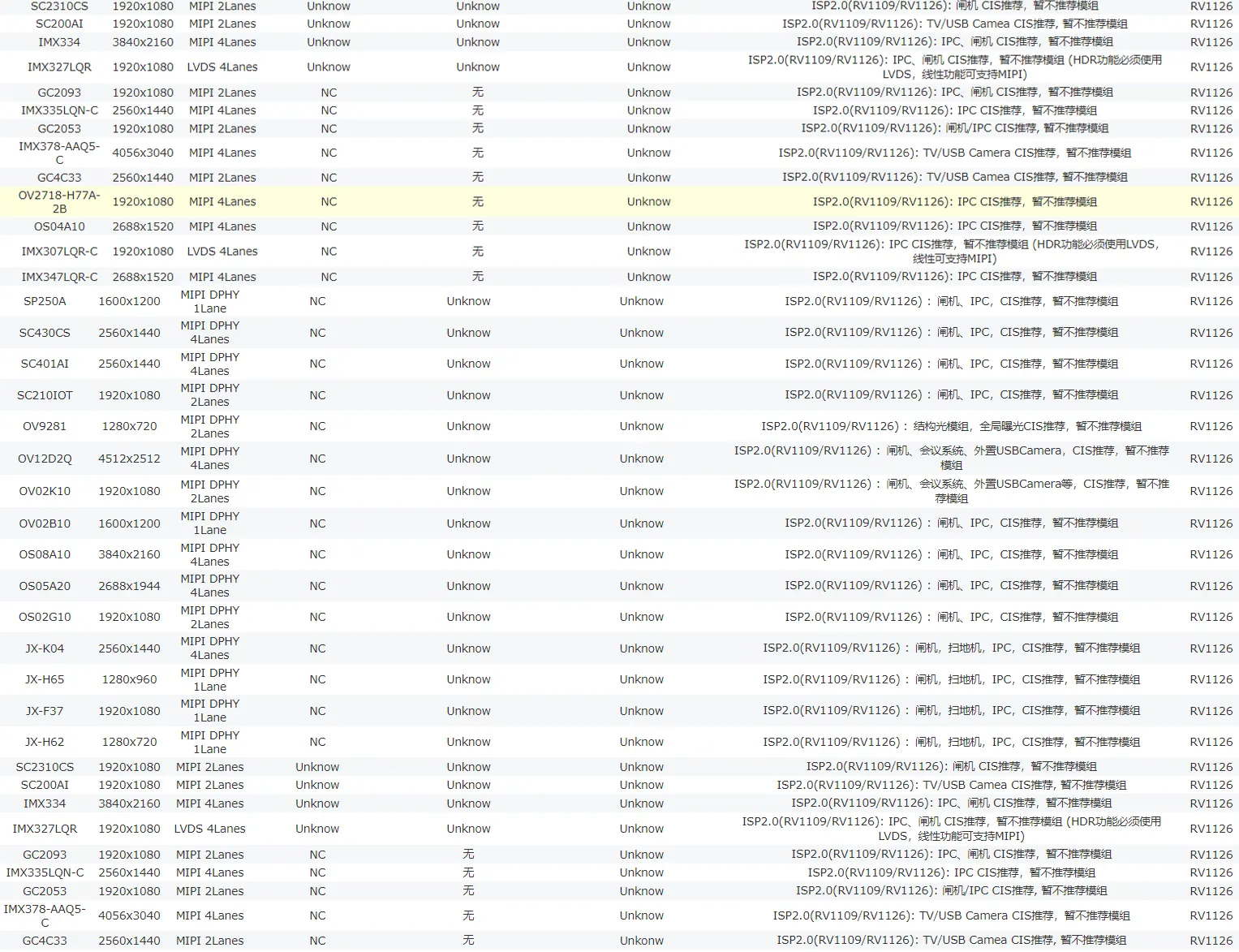

Domanda 1: Quali driver della fotocamera sono supportati dall'SDK?

Risposta 1:

Domanda 2: Quali driver video MIPI DSI sono supportati dall'SDK?

Risposta 2: Il debug di MIPI DSI viene eseguito in base alla schermata specifica. Si prega di verificare l'immagine qui sotto.

Abbiamo un'altra scheda opzionale; fateci sapere se ne avete bisogno.

1.1 Panoramica

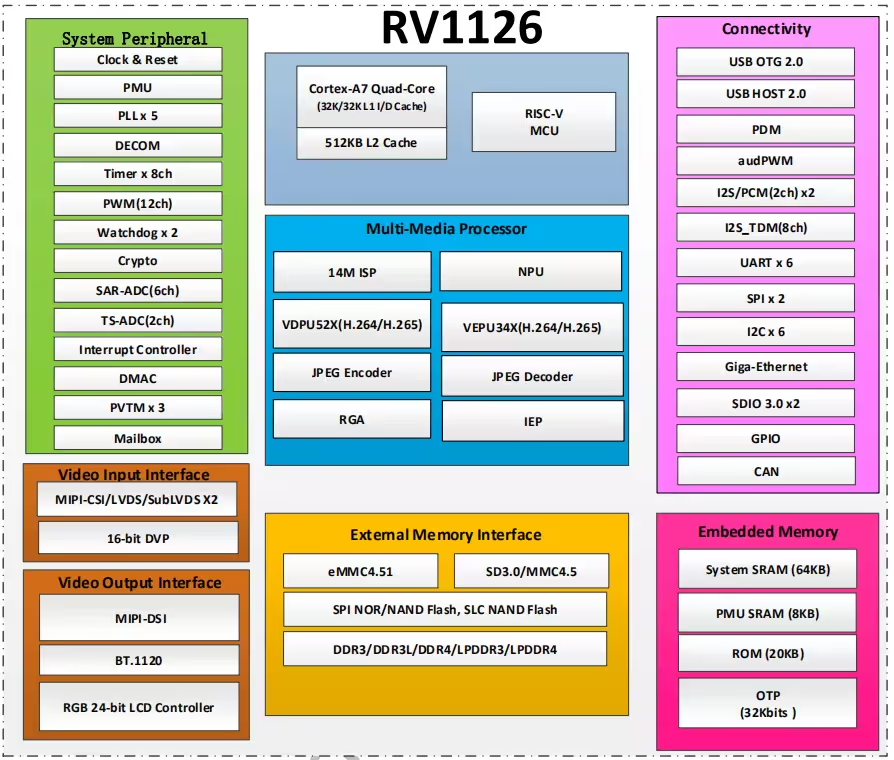

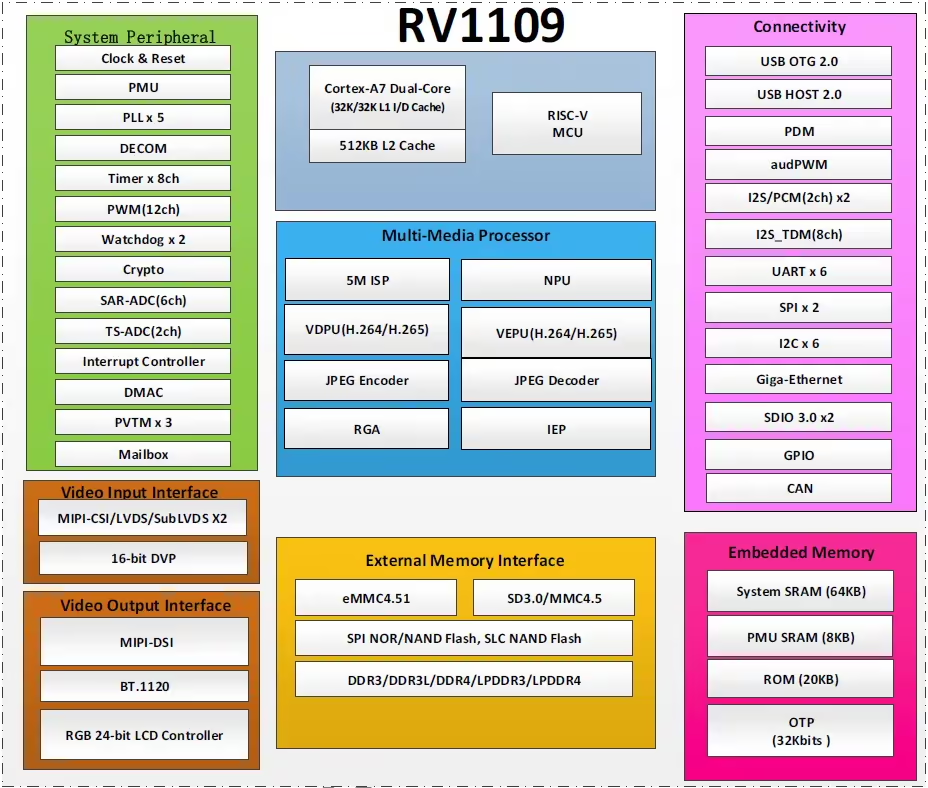

RV1126 è un SoC con processore di visione ad alte prestazioni per IPC/CVR, soprattutto per le applicazioni relative all'IA. Si basa su un core ARM Cortex-A7 quad-core a 32 bit che integra NEON e FPU. C'è una I-cache da 32 KB e una D-cache da 32 KB per ciascun core e una cache L2 unificata da 512 KB. La NPU integrata supporta il funzionamento ibrido INT8/INT16 e la potenza di calcolo è fino a 2,0 TOP. Inoltre, con la sua forte compatibilità, i modelli di rete basati su una serie di framework come TensorFlow/MXNet/PyTorch/Caffe possono essere facilmente convertiti.<fr>

RV1126 introduce anche un ISP da 14 megapixel totalmente basato su hardware di nuova generazione (processore di segnale di immagine) e post-processore. Implementa molti acceleratori di algoritmi solitamente utilizzati in IPC e CVR, come l'HDR, 3A funziona (AE, DI, AWB), LSC, 3DNR, 2DNR, affilatura, sfocatura, correzione fisheye, correzione gamma, rilevamento dei punti caratteristica e così via. Sono tutti elaborazione in tempo reale. Collaborazione con due MIPI CSI (o LVDS/SubLVDS) e un DVP (BT.601/BT.656/BT.1120) interfaccia, gli utenti possono creare un sistema che riceve dati video da 3 sensori della fotocamera contemporaneamente.

Il codificatore video incorporato in RV1126 supporta la codifica UHD H.265/H.264. Supporta anche la codifica multi-stream, fino a un 4Kp30 e un 1080p30 simultanei. Con l'aiuto di questa funzione, il video dalla telecamera può essere codificato con una risoluzione maggiore e archiviato nella memoria locale e trasferito contemporaneamente a un altro video a risoluzione inferiore nell'archiviazione cloud. Il decoder video H.264/H.265 in RV1126 supporta 4Kp30 per H.264 e H.265.

Oltre al precedente blocco multimediale ad alte prestazioni, RV1126 contiene anche un audio ricco, memoria, e altre interfacce periferiche come I2C, SPI, PWM, e così via. Questi possono aiutare gli utenti ad aggiungere più sensori o altre periferiche all'intero sistema per migliorare la flessibilità e l'espandibilità.

RV1126 ha una DRAM esterna ad alte prestazioni (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133) in grado di sostenere larghezze di banda di memoria impegnative.

1.2 Caratteristiche

Le funzionalità elencate di seguito che possono essere o meno presenti in un prodotto reale possono essere soggette ai requisiti di licenza di terze parti. Si prega di contattare Rockchip per le configurazioni effettive delle funzioni del prodotto e i requisiti di licenza.

1.2.1 Processore di applicazioni

Quad-core Cortex-A7

Implementazione completa del set di istruzioni dell'architettura ARM v7-A, ARM Neon Advanced SIMD

Neon e FPU integrati separatamente

32KB L1 I-Cache e 32KB L1 D-cache per CPU Cortex-A7

Cache L2 unificata da 512 KB per Quad-Core Cortex-A7

Tecnologia TrustZone supportata

Domini di alimentazione separati per il sistema principale della CPU per supportare l'interruttore di alimentazione interno e l'attivazione/disattivazione esterna in base al diverso scenario dell'applicazione

PD_CPU0: 1st Cortex-A7 + Neon + FPU + Cache I/D L1

PD_CPU1: 2nd Cortex-A7 + Neon + FPU + Cache I/D L1

PD_CPU2: 3rd Cortex-A7 + Neon + FPU + Cache I/D L1

PD_CPU3: 4th Cortex-A7 + Neon + FPU + Cache I/D L1

Un dominio di tensione isolato per supportare DVFS

1.2.2 Video Interfaccia di ingresso

Interfaccia e processore di ingresso video

Due interfacce MIPI CSI/LVDS/SubLVDS, 4 corsie ciascuno, La velocità massima dei dati MIPI CSI è di 2,5 Gbps/corsia, La velocità dati massima di LVDS/SublVDS è 1 Gbps/lane

Su interfaccia DVP standard a 8/10/12/16 bit, dati in ingresso fino a 150 MHz

Supporta le interfacce BT.601/BT.656 e BT.1120 VI

Supporta la polarità di pixel_clk、hsync、vsync configurabile

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

ISP

La risoluzione massima è 14Mpixel(4416×3312)

Ingresso DVP: ITU-R BT.601/656/1120 con raw8/raw10/raw12/raw16, YUV422

Ingresso MIPI: Corsia dati RX x1/x2/x4, crudo8/grezzo10/grezzo12, YUV422

3A: includere AE/istogramma, DI, Uscita statistica AWB

FPN: Risolto il problema con la rimozione del rumore di pattern

BLC: Correzione del livello di nero

DPCC: Correzione del cluster di pixel dei difetti statici/dinamici

LSC: Correzione dell'ombreggiatura della lente

Bayer n: De-noising Bayer-raw, 2DNR

HDR: 3-/2-Frame Merge in High-Dynamic Range

TMO: 3-/2-Frame Merge Video Tone mapping

WDR: Mappatura dei toni ad ampia gamma dinamica di un fotogramma

Debayer: Demosaico adattivo avanzato con correzione dell'aberrazione cromatica

CCM/CSM: Matrice di correzione del colore; RGB2YUV ecc.

Gamma: Correzione fuori gamma

Sfocatura/Migliora: Dehaze automatico e miglioramento dei bordi

3DLUT: 3Tavolozza dei colori D-Lut per il cliente

LDCH: Distorsione della lente in direzione orizzontale

Scala di uscita*3: supporto scalare il livello*3(W0<3264; W1<1280; W2<1280)

Scala di uscita*2: supporto scalare il livello*2(W0<1920; W1<1920)

Uscita (FBC): supporto YUV422/420 con compressione frame buffer

3DNR: Riduzione avanzata del rumore temporale in YUV

2DNR: Riduzione avanzata del rumore spaziale in YUV

Nitido: Nitidezza dell'immagine & Miglioramento bordo in YUV

ORB: BREVE Orientato Veloce e Ruotato, un metodo di rilevamento dei punti caratteristici

FEC: la maggiore distorsione dell'obiettivo e la correzione dell'occhio di pesce

CGC: Compressione della gamma di colori, Conversione gamma completa/limite YUV

1.2.3 Video codec

Decodificatore video

Decodifica in tempo reale di H.264 e H.265

Profilo Main e Main10 per H.265, fino a livello 5.0 e 4096×2304 a 30 fps

Linea di base, principale, alto, alto10 e alto 4:2:2(senza MBAFF), fino a livello 5.1 e 4096×2304 a 30 fps

Codificatore video

Codifica video UHD H.265/H.264 in tempo reale

Frame I/P e riferimento SmartP.

Modalità di controllo della velocità a cinque bit (CBR, VBR, FixQp, AVBR, e QpMap)

Fino a 100 Velocità in bit di uscita Mbit/s

Supporta il ROI(Senza limiti) codifica;

Alto profilo per H.264, fino a livello 5.1 e 4096×2304 a 30 fps

Profilo principale per H.265, fino a livello 5.0 e 4096×2304 a 30 fps

Supporta la codifica multi-stream

3840 x 2160 @ 30 fps + 1080codifica p@30 fps

3840 x 2160@30 codifica + 3840 x 2160 @ 30 fps decodifica

Immettere il formato dei dati:

YCbCr 4:2:0 planare

YCbCr 4:2:0 semiplanare

YCbYCr 4:2:2

CbYCrY 4:2:2 interfogliato

RGB444 e BGR444

RGB555 e BGR555

RGB565 e BGR565

RGB888 e BRG888

RGB101010 e BRG101010

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

Un dominio di tensione isolato per supportare DVFS

1.2.4 CODICE JPEG

Codificatore JPEG

Linea di base (sequenziale DCT)

La dimensione dell'encoder va da 96×96 a 8192×8192(67Megapixel)

Fino a 90 milioni di pixel al secondo

Decodificatore JPEG

La dimensione del decoder va da 48×48 a 8176×8176(66.8Megapixel)

Fino a 76 milioni di pixel al secondo

1.2.5 Unità di processo neurale

Motore di accelerazione della rete neurale con prestazioni di elaborazione fino a 2.0 TOP

Supporto intero 8, numero intero 16 operazione di convoluzione

Supportare i framework di deep learning: TensorFlow, TF-lite, Pitorcia, Caffè, ONNX, Rete MX, Difficile, Rete oscura

Supporta l'API OpenVX

Un dominio di tensione isolato per supportare DVFS

1.2.6 Organizzazione della memoria

Memoria interna su chip

BootRom

SYSTEM_SRAM nel dominio della tensione di VD_LOGIC

PMU_SRAM nel dominio della tensione di VD_PMU per applicazioni a bassa potenza

Memoria esterna fuori chip

DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133①

Flash SPI

eMMC

Scheda SD

Nand Flash asincrono

1.2.7 Memoria interna

BootRom interno

Supporta l'avvio del sistema dal seguente dispositivo:

Interfaccia Flash FSPI

Interfaccia eMMC

Interfaccia SDMMC

Interfaccia Nand asincrona

Supporta il download del codice di sistema dalla seguente interfaccia:

Interfaccia USB OTG (Modalità dispositivo)

SYSTEM_SRAM

Dimensioni: 64KB

PMU_SRAM

Dimensioni: 8KB

1.2.8 Memoria esterna o dispositivo di archiviazione

Interfaccia di memoria dinamica (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133)

Compatibile con gli standard JEDEC

Compatibile con DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133

Supporta la larghezza dei dati a 32 bit, 2 ranghi (il chip seleziona), max 4 GB di spazio di indirizzamento per rango, lo spazio di indirizzamento totale è di 4 GB (max)

Modalità a basso consumo, come lo spegnimento e l'aggiornamento automatico per SDRAM

Interfaccia eMMC

Compatibile con l'interfaccia iNAND standard

Compatibile con le specifiche eMMC 4.51

Supporta tre larghezze di bus dati: 1-po, 4-bit o 8 bit

Supporto fino a HS200; ma non supporta la coda CMD

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

Interfaccia SD/MMC

Compatibile con SD3.0, MMC ver4.51

La larghezza del bus dati è di 4 bit

Interfaccia flash seriale flessibile(FSPI)

Supporta il trasferimento di dati da/verso un dispositivo flash seriale

Supporto x1, x2, modalità x4 bit di dati

Supporto 2 patatine selezionate

Interfaccia Nand Flash

Supporto asincrono e flash

La larghezza del bus dati è di 8 bit

Supporto 1 selezione del chip

Supporta LBA e flash

Hardware ECC fino a 16 bit/1 KB

Supporta la temporizzazione dell'interfaccia configurabile

1.2.9 Componente di sistema

RISC-V MCU

Microcontrollore a 32 bit con RISC -V ISA

Architettura di Harvard, Istruzione separata, e memorie dati

Il set di istruzioni è RV32I con estensioni M e C

Controller di interrupt programmabile integrato (IPIC), tutto 123 Le linee IRQ collegate a GIC per Cortex-A7 si collegano anche a RISC –V MCU

Controller di debug integrato con interfaccia JTAG

CRU (orologio & unità di ripristino)

Supporta il controllo del clock gating per i singoli componenti

Un oscillatore con ingresso di clock a 24 MHz

Supporta il controllo globale del soft reset per l'intero chip, anche soft-reset individuale per ogni componente

PMU (unità di gestione dell'alimentazione)

Supporto 5 domini di tensione separati VD_CORE/VD_LOGIC/VD_PMU/VD_NPU/VD_VEPU

Supporto 14 domini di potere separati, che può essere acceso/spento dal software in base a diverse scene dell'applicazione

Molteplici modalità di lavoro configurabili per risparmiare energia in base a diverse frequenze o controllo automatico del clock gating o controllo on/off del dominio di alimentazione

Timer

Supporto 6 64bit-timer con l'operazione basata su interrupt per applicazioni non sicure

Supporto 2 64bit-timer con il funzionamento basato su interrupt per applicazioni sicure

Supporta due modalità operative: conteggio a corsa libera e definito dall'utente

Supporta lo stato di lavoro del timer verificabile

PWM

Supporto 12 PWM su chip (PWM0 ~ PWM11) con l'operazione basata su interrupt

L'operazione programmabile prescalata sull'orologio bus e quindi ulteriormente ridimensionata

Funzione timer/contatore a 32 bit incorporata

Supporta la modalità di acquisizione

Supporta la modalità continua o la modalità one-shot

Fornisce la modalità di riferimento ed emette varie forme d'onda del duty-cycle

Ottimizzato per l'applicazione IR per PWM3, PWM7, e PWM11

Watchdog

Contatore watchdog a 32 bit

Il contatore esegue il conto alla rovescia da un valore preimpostato a 0 per indicare il verificarsi di un timeout

WDT può eseguire due tipi di operazioni quando si verifica il timeout:

Genera un ripristino del sistema

Primo, generare un interrupt e se questo non viene cancellato dalla routine di servizio prima che si verifichi un secondo timeout, generare un ripristino del sistema

Durata dell'impulso di ripristino programmabile

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

Totalmente 16 intervalli definiti del periodo di timeout principale

Un unico watchdog per applicazioni non sicure

Un Watchdog per un'applicazione sicura

Controller di interruzione

Supporto 128 Sorgenti di interrupt SPI in ingresso da diversi componenti

Supporto 16 interrupt attivati dal software

Due uscite di interruzione (nFIQ e nIRQ) separatamente per ogni Cortex-A7, entrambi sono sensibili di basso livello

Supporta diverse priorità di interruzione per ciascuna sorgente di interruzione, e sono sempre programmabili via software

DMAC

DMA basato sulla programmazione di microcodice

La funzione DMA dell'elenco collegato è supportata per completare il trasferimento scatter-gather

Supporta tipi di trasferimento dati da memoria a memoria, da memoria a periferica, periferica a memoria

Segnala il verificarsi di vari eventi DMA utilizzando i segnali di uscita di interruzione

Un controller DMA integrato per il sistema

Funzionalità DMAC:

Supporto 8 canali

27 richieste hardware dalle periferiche

2 interrompe l'uscita

Supporta la tecnologia TrustZone e lo stato di sicurezza programmabile per ciascun canale DMA

Sistema sicuro

Motore di cifratura

Supporta la cifratura SM2/SM3/SM4

Supporto SHA-1, SHA-256/224, SHA-512/384, e MD5 con imbottitura hardware

Elemento dell'elenco dei collegamenti di supporto (LLI) Trasferimento DMA

Supporta la crittografia AES-128 AES-256 & decifrare la cifra

Supporta la modalità AES ECB/CBC/OFB/CFB/CTR/CTS/XTS

Supporto DES & Crittografare TDES & decifrare la cifra

Supporta la modalità DES/TDES ECB/CBC/OFB/CFB

Supporto fino a 4096 bit Operazioni matematiche PKA per RSA/ECC

Supporta una configurazione fino a 8 canali

Supporto fino a 256 bit di uscita TRNG

Supporta la codifica dei dati per tutti i tipi di DDR

Supporta OTP sicuro

Supporta il debug sicuro

Supporta un sistema operativo sicuro

Cassetta postale

Una cassetta postale nel SoC per il servizio di comunicazione A7 e RISC-V MCU

Supporta quattro elementi della casella di posta per casella di posta, ogni elemento include una parola di dati, un registro di parole di comando, e un bit flag che può rappresentare un interrupt

Fornire 32 registri di blocco per il software da utilizzare per indicare se la casella di posta è occupata

BAMBINI

Supporto per la decompressione dei file GZIP

Supporto per la decompressione dei file LZ4, inclusa la struttura generale del formato frame LZ4 e il formato frame legacy.

Supporto per la decompressione dei dati in formato sgonfia

Supporto per la decompressione dei dati in formato ZLIB

Supporta l'interruzione completa e l'uscita di interruzione di errore

Supporta il controllo Hash32 nel processo di decompressione LZ4

Supporta la funzione di dimensione limite dei dati decompressi per evitare che la memoria venga distrutta in modo dannoso durante il processo di decompressione

Software di supporto per interrompere il processo di decompressione

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

1.2.10 Motore grafico

Motore grafico 2D (RGA):

Formati sorgente:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planare, YUV420 semiplanare

YUV422 planare, YUV422 semiplanare

YUV 10 bit per YUV420/422 semiplanare

BPP8, BPP4, BPP2, BPP1

Formati di destinazione:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planare, YUV420 semiplanare

YUV422 planare, YUV422 semiplanare

Conversione del formato pixel, BT.601/BT.709

Risoluzione massima: 8192×8192 sorgente, 4096×4096 destinazione

BitBlt

Due sorgenti BitBLT:

A+B=B solo BitBLT, Un supporto ruota e scala quando B è fisso

A+B=C seconda sorgente (B) ha lo stesso attributo di (C) più funzione di rotazione

Riempimento colore con riempimento sfumato, e riempimento a motivo

Elastico e termoretraibile ad alte prestazioni

Espansione monocromatica per il rendering del testo

Nuova alfa per pixel completa (colore/canale alfa separatamente)

Modalità di fusione Alpha, incluso Java 2 Regole di miscelazione del compositing Porter-Duff, chiave cromatica, maschera modello, dissolvenza

Operazione di dithering

0, 90, 180, 270-rotazione dei gradi

specchio x, y-specchio, e operazione di rotazione

Processore di miglioramento dell'immagine (PEI):

Formato immagine

Immettere i dati: YUV420 / YUV422, semi-planare/planare, Scambio UV

Dati di output: YUV420 / YUV422, semiplanare, Scambio UV, Modalità piastrella

Conversione del campionamento verso il basso YUV da 422 a 420

Risoluzione massima per immagini dinamiche fino a 1920×1080

De-interlacciamento

1.2.11 Interfaccia di visualizzazione

Uno fino a 24 bit interfaccia di uscita video parallela RGB

Un'interfaccia di uscita video BT.1120

Un'interfaccia MIPI DSI a 4 corsie, fino a 1 Gbps per corsia

Fino a 1080p@60fps

1.2.12 Processore di uscita video (CGC)

Fino a 1920×1080 a 60 fps

Strato multiplo

Livello di sfondo

Livello Win0

Strato Win2

Formato di input: RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444

1/8 a 8 motore di ridimensionamento e aumento

Supporta la visualizzazione virtuale

256 miscelazione alfa di livello (supporto alfa premoltiplicato)

Tasto colore Trasparenza

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

RGB2YCbCr (BT.601/BT.709)

Supporto multiregione

Strato Win0 e overlay Win2 intercambiabili

Supporta la sovrapposizione del dominio RGB o YUV

BCSH (Luminosità, Contrasto, Saturazione, Regolazione della tonalità)

BCSH: YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

BCSH: RGB2YCbCr (BT.601/BT.709)

Supporta la regolazione della gamma

Supporta dither down allegro RGB888to666 RGB888to565 & dithering verso il basso FRC (configurabile) RGB888to666

Display vuoto e nero

1.2.13 Interfaccia audio

I2S0 con 8 canali

Fino a 8 canali TX e 8 canali RX percorso

Risoluzione audio da 16 bit a 32 bit

Frequenza di campionamento fino a 192 KHz

Fornisce modalità di lavoro master e slave, software configurabile

Supporto 3 Formati I2S (normale, giustificato a sinistra, giustificato a destra)

Supporto 4 formati PCM (presto, tardi1, tardi2, tardi3)

Le modalità I2S e PCM non possono essere utilizzate contemporaneamente

I2S1/I2S2 con 2 canali

Fino a 2 canali per TX e 2 canali RX percorso

Risoluzione audio da 16 bit a 32 bit

Frequenza di campionamento fino a 192 KHz

Fornisce modalità di lavoro master e slave, software configurabile

Supporto 3 Formati I2S (normale, giustificato a sinistra, giustificato a destra)

Supporto 4 formati PCM (presto, tardi1, tardi2, tardi3)

I2S e PCM non possono essere utilizzati contemporaneamente

PDM

Fino a 8 canali

Risoluzione audio da 16 bit a 24 bit

Frequenza di campionamento fino a 192 KHz

Supporta la modalità di ricezione master PDM

TDM

Supporto fino a 8 canali per TX e 8 canali per il percorso RX

Risoluzione audio da 16 bit a 32 bit

Frequenza di campionamento fino a 192 KHz

Fornisce modalità di lavoro master e slave, software configurabile

Supporto 3 Formati I2S (normale, giustificato a sinistra, giustificato a destra)

Supporto 4 formati PCM (presto, tardi1, tardi2, tardi3)

Audio PWM

Supporta la conversione del formato PCM in PWM

Frequenza di campionamento fino a 16x

Supporta l'interpolazione lineare per il sovracampionamento 2x/4x/8x/16

Supporto 8/9/10/11 bit mascherabile uscita PWM canale L/R

Codec audio digitale

Supporta ADC digitale a 3 canali

Supporta DAC digitale a 2 canali

Supporta l'interfaccia I2S/PCM

Supporta la modalità I2S/PCM master e slave

Supporta la trasmissione audio a 4 canali in modalità I2S

Supporta la ricezione audio a 2 canali in modalità I2S

Supporta la trasmissione o la ricezione di audio a 2 canali in modalità PCM

Supporta una risoluzione di campionamento di 16~24 bit sia per ADC digitale che DAC digitale

<stile intervallo =”colore: #ffffff;”>Scheda tecnica RV1126 Rev 1.4</campata>

Sia l'ADC digitale che il DAC digitale supportano tre gruppi di frequenze di campionamento. Gruppo 0 sono 8 kHz/16 kHz/32 kHz/64 kHz/128 kHz, gruppo 1 sono 11.025khz/22.05khz/44.1khz/88.2khz/176.4khz e gruppo 2 sono 12khz/24khz/48khz/96khz/192khz

La banda passante dei filtri ADC digitali è 0,45625*fs

Supporta l'ondulazione della banda passante dell'ADC digitale entro +/-0,1dB

La banda di arresto dei filtri ADC digitali è 0,5*fs

Supporta l'attenuazione della banda di arresto dell'ADC digitale di almeno 60 dB

Supporta il controllo del volume sia per l'ADC digitale che per il DAC digitale

Supporta il controllo automatico del livello (ALC)e noise gate per ADC digitale

Supporta la comunicazione con il codec analogico tramite il bus I2C

1.2.14 Connettività

Interfaccia SDIO

Compatibile con il protocollo SDIO3.0

Ampiezza del bus dati a 4 bit

Controller ethernet GMAC 10/100/1000M

Supporta velocità di trasferimento dati 10/100/1000 Mbps con le interfacce RGMII

Supporta velocità di trasferimento dati di 10/100 Mbps con le interfacce RMII

Supporto per operazioni full-duplex e half-duplex Supporto per TCP segmentation offload (TSO) e Offload della segmentazione UDP (USO) accelerazione della rete<fr>

USB 2.0 Ospite

Compatibile con USB 2.0 specifica

Supporta l'alta velocità(480Mbps), piena velocità(12Mbps) e a bassa velocità(1.5Mbps) modalità

Supporto delle specifiche avanzate dell'interfaccia del controller host (EHC), Revisione 1.0

Supporta la specifica dell'interfaccia del controller host aperto (OHCI), Revisione 1.0a

USB 2.0 OTG

Specifiche compatibili

Specifiche del bus seriale universale, Revisione 2.0

Interfaccia controller host estensibile per Universal Serial Bus (xHCI), Revisione 1.1

Supporto per il controllo/bulk/interruzioni/trasferimento isocrono

Interfaccia SPI

Supporto 2 Controller SPI, supporta due output di selezione del chip

Supporta la modalità seriale-master e seriale-slave, configurabile tramite software

Interfaccia I2C

Supporto 6 Interfacce I2C(I2C0-I2C5)

Supporta la modalità indirizzo a 7 bit e 10 bit

Frequenza di clock programmabile da software

I dati sul bus I2C possono essere trasferiti a velocità fino a 100.000 bit/s in modalità Standard, fino a 400k bit/s in modalità Veloce, o fino a 1 m bit/s in modalità Fast-mode Plus

Interfaccia UART

Supporto 6 Interfacce UART (UART0-UART5)

Supporta 5 bit, 6po, 7po, e i dati seriali a 8 bit trasmettono o ricevono

Bit di comunicazione asincroni standard come start, fermare, e parità

Supporta diversi clock di input per il funzionamento UART per ottenere una velocità di trasmissione fino a 4Mbps

Supporta la modalità di controllo del flusso automatico(tranne UART2)

1.2.15 Altri

Gruppi multipli di GPIO

Tutti i GPIO possono essere utilizzati per generare un interrupt

Supporto livello trigger e edge trigger interrupt

Supporta la polarità configurabile dell'interruzione del trigger di livello

Supporta il fronte di salita configurabile, bordo discendente, ed entrambi i fronti si interrompono

Supporta la direzione di trazione configurabile (un debole pull-up e un debole pull-down)

<forte>Scheda tecnica RV1126 Rev 1.4</forte>

Supporta la potenza dell'unità configurabile

Sensore di temperatura (TS-ADC)

Supporta la modalità definita dall'utente e la modalità automatica

In modalità definita dall'utente, start_of_conversion può essere controllato completamente dal software, e può anche essere generato dall'hardware.

In modalità automatica, la temperatura di allarme(alta/bassa temperatura) l'interruzione può essere configurabile

In modalità automatica, la temperatura di ripristino del sistema è configurabile

Supporto a 2 canale TS-ADC (utilizzato rispettivamente per CPU e NPU), i criteri di temperatura di ciascun canale possono essere configurati

Intervallo di temperatura -40~125°C e risoluzione della temperatura di 5°C

ADC SAR a 12 bit fino a 732 Frequenza di campionamento S/s

ADC ad approssimazione successiva (SAR ADC)

Risoluzione a 10 bit

Frequenza di campionamento fino a 1MS/s

6 canali di ingresso single-ended

OTP

Il supporto di 32 Kbit di spazio e uno spazio di indirizzi di 4k superiore è una parte non sicura.

Supporta la lettura e la programmazione della maschera di parole in un modello sicuro

Durata del programma di supporto da 1 a 32 po

Supporto per operazioni di lettura solo a 8 bit

È possibile leggere lo stato del programma e della lettura

Il programma non riesce a indirizzare il record

Tipo di pacchetto

FCCSP 409 pin (corpo: 14mm x 14 mm; Dimensione della palla: 0.3mm; campo di palla: 0.65mm)

Appunti:

①: DDR3/DDR3L/DDR4/LPDDR3/LPDDR4 non vengono utilizzati contemporaneamente

Scaricare

RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=sharing

SDK

https://drive.google.com/file/d/1CCNWHNNVi8FVG6UXNgrMDYsZx3SrpFyr/view?usp=sharing

Scheda dati

Scheda tecnica RV1126-Vcan1748

RV1126 RV1109 Avvio rapido

Rockchip_RV1126_RV1109_Quick_Start_Linux_IT

Guida per sviluppatori Rockchip RockX_SDK

Personalizzazione della scheda di sviluppo RV1126

WI-FI & Bluetooth

Un'altra fotocamera di marca per sostituire Sony IMX415

Un ingresso per fotocamera USB, Trasferisce lo streaming video su un altro computer tramite il modulo WIFI

Recensioni

Non ci sono ancora recensioni.