Como el chip RV1126 ha sido descontinuado, Recomendamos IPC2188 como solución de reemplazo..

Por favor haga clic en el enlace a continuación para obtener más detalles.: Más información sobre IPC2188

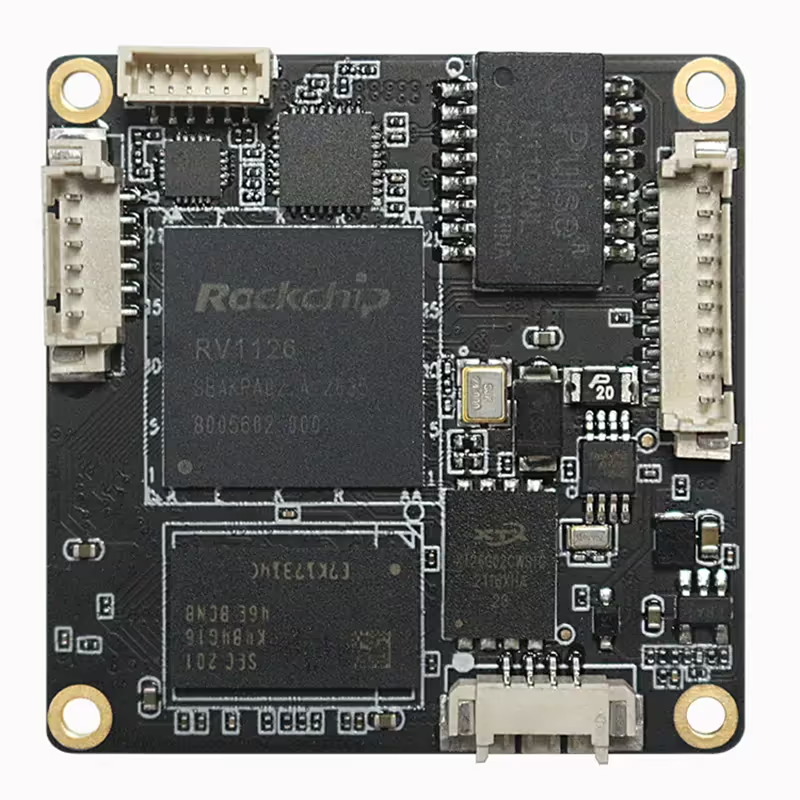

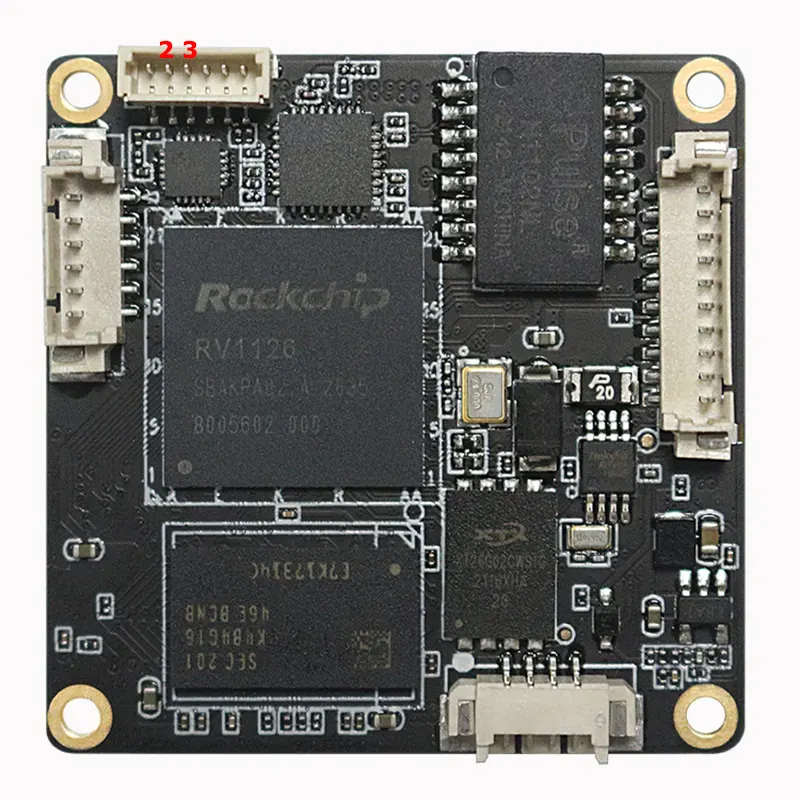

Rockchip RV1126 Placa de evaluación de desarrollo Placa base IPC AI SDK Kit de desarrollo de software

Tabla de contenido

Galería

Aplicaciones del producto

CIP inteligente, Máquina de panel de reconocimiento facial, Cámara de captura de rostro, Timbre de vídeo, Sin red, y sin cámara de energía, Expreso de mano, Navegacion GPS, Interfaz hombre-máquina, Equipo de vigilancia, Cápsula de drones, Sistema de videoconferencia, etc..

Quiere trabajar con el módulo de cámara de lente Sony IMX415?

Descarga el SDK

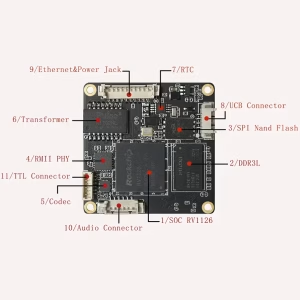

Especificación de la vista frontal

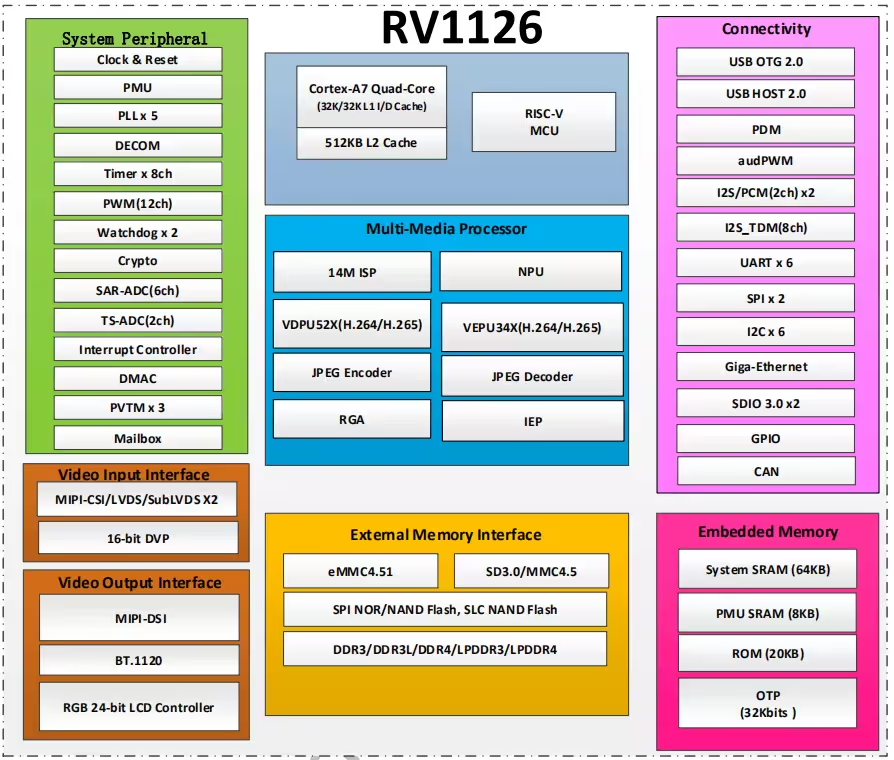

1. SOC RV1126, Pin a Pin compatible con RV1109;

|

Pin1 |

VCC5V0_OTG |

|

Pin2 |

OTG_DM |

|

Pin3 |

OTG_DP |

|

pin4 |

GND |

9.Ethernet&Conector de alimentación

|

Pin1 |

TX+ |

Pin6 |

RX- |

|

Pin2 |

TX- |

Pin7 |

POE78 |

|

Pin3 |

RX+ |

Pin8 |

POE78 |

|

pin4 |

POE45 |

Pin9 |

GND |

|

Pin5 |

POE45 |

Pin10 |

VCC12V_DCIN |

10. Conector de audio

|

Pin1 |

LED1/PHYAD1 |

|

Pin2 |

LED0 / PHYAD0 |

|

Pin3 |

REINICIAR |

|

pin4 |

MICP |

|

Pin5 |

GND |

|

Pin6 |

SALIDA DE LÍNEA |

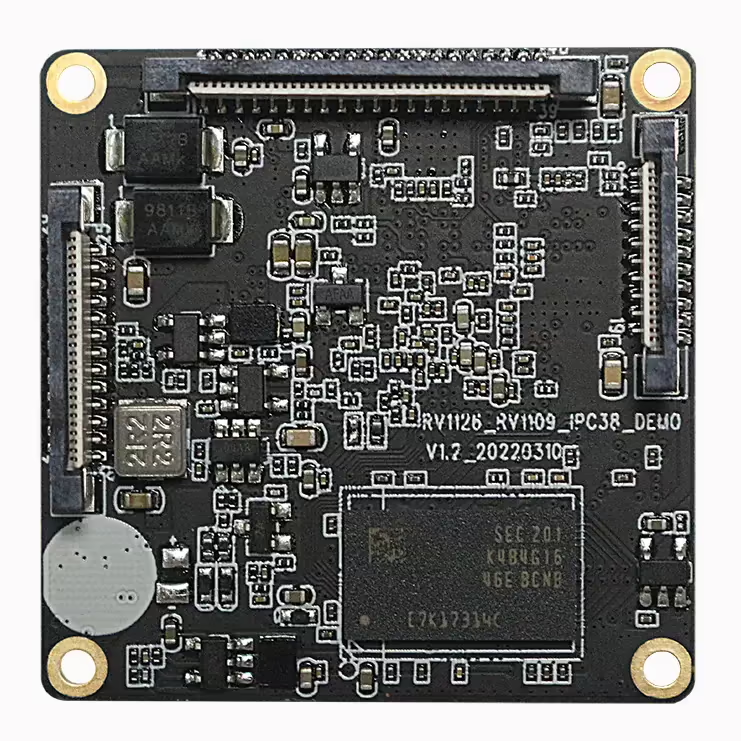

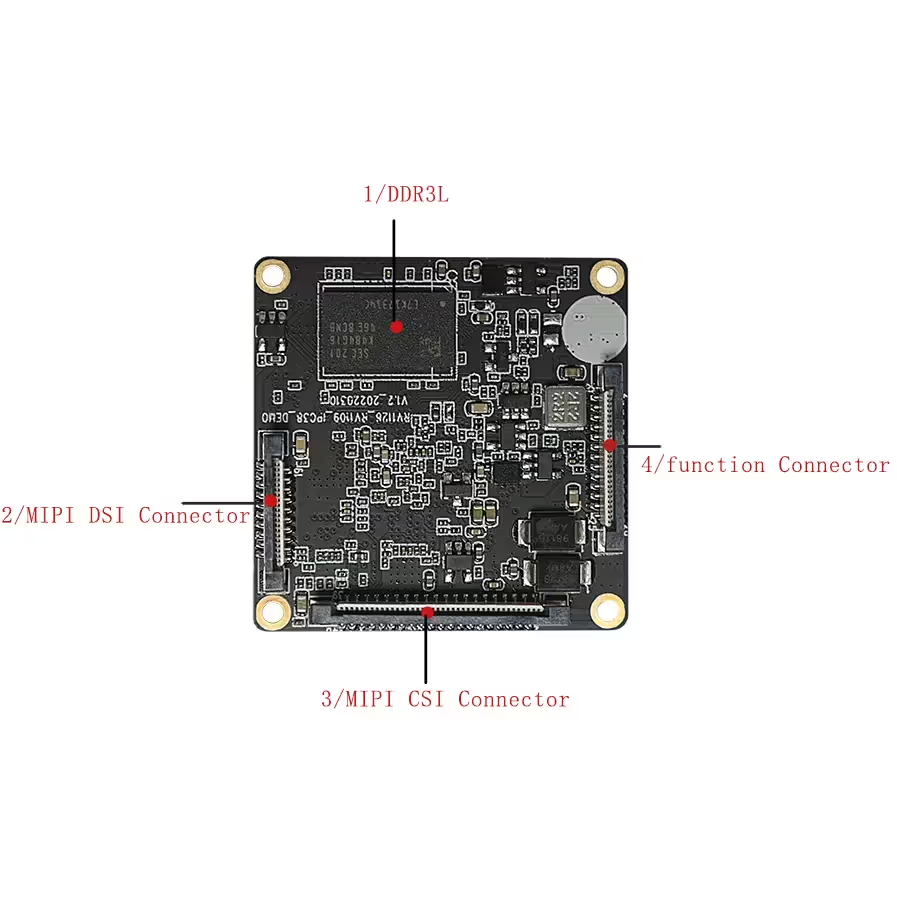

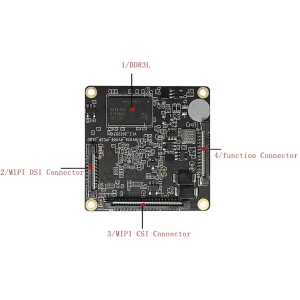

Especificación de la vista posterior

1.DDR3L (Samsung K4B4G1646E BCNB)

Se adjunta un DDR3 de 4 Gbit en la parte delantera y trasera de toda la placa, con un total de 8G bits;

2.Conector MIPI DSI

|

Pin1 |

IRQ |

Pin11 |

MIPI_DSI_D3N |

|

Pin2 |

PWR_ES |

Pin12 |

MIPI_DSI_D3P |

|

Pin3 |

RST |

Pin13 |

MIPI_DSI_D0N |

|

pin4 |

I2C3_SDA |

Pin14 |

MIPI_DSI_D0P |

|

Pin5 |

I2C3_SCL |

Pin15 |

GND |

|

Pin6 |

GND |

Pin16 |

MIPI_DSI_CLKN |

|

Pin7 |

MIPI_DSI_D2P |

Pin17 |

MIPI_DSI_CLKP |

|

Pin8 |

MIPI_DSI_D2N |

Pin18 |

GND |

|

Pin9 |

MIPI_DSI_D1P |

Pin19 |

VCC_12V |

|

Pin10 |

MIPI_DSI_D1N |

Pin20 |

VCC_12V |

3.Conector MIPI CSI

|

Pin1 |

VCC3V3_SYS |

Pin21 |

MIPI_CSI_RX0_D1N |

|

Pin2 |

VCC3V3_SYS |

Pin22 |

MIPI_CSI_RX0_D0P |

|

Pin3 |

SPI0_CLK |

Pin23 |

MIPI_CSI_RX0_D0N |

|

pin4 |

LED_PWM |

Pin24 |

GND |

|

Pin5 |

SPI0_CS0N |

Pin25 |

MIPI_CSI_CLK0 |

|

Pin6 |

SPI0_MISO |

Pin26 |

GND |

|

Pin7 |

SPI0_MOSI |

Pin27 |

PWM8 |

|

Pin8 |

I2C1_SDA |

Pin28 |

IRC_AIN |

|

Pin9 |

I2C1_SCL |

Pin29 |

PWM11 |

|

Pin10 |

MIPI_RX0_PDN |

Pin30 |

PWM9 |

|

Pin11 |

MIPI_RX0_RST |

Pin31 |

IRC_BIN |

|

Pin12 |

GND |

Pin32 |

ZOOM_ES |

|

Pin13 |

MIPI_CSI_RX0_CLKP |

Pin33 |

PWM10 |

|

Pin14 |

MIPI_CSI_RX0_CLKN |

Pin34 |

P-IRIS_EN |

|

Pin15 |

GND |

Pin35 |

FOCUS_ES |

|

Pin16 |

MIPI_CSI_RX0_D2P |

Pin36 |

ADC_IN |

|

Pin17 |

MIPI_CSI_RX0_D2N |

Pin37 |

GND |

|

Pin18 |

MIPI_CSI_RX0_D3P |

Pin38 |

VCC_1V8 |

|

Pin19 |

MIPI_CSI_RX0_D3N |

Pin39 |

VCC_12V |

|

Pin20 |

MIPI_CSI_RX0_D1P |

Pin40 |

VCC_12V |

4.Conector de función

|

Pin1 |

HOST_DM |

Pin14 |

SDMMC0_D0 |

|

Pin2 |

HOST_DP |

Pin15 |

SDMMC0_CLK |

|

Pin3 |

GND |

Pin16 |

SDMMC0_D3 |

|

pin4 |

GND |

Pin17 |

RS485_CTL |

|

Pin5 |

ALARMA_EN |

Pin18 |

UART3_RX_485 |

|

Pin6 |

SDMMC0_DET |

Pin19 |

UART3_TX_485 |

|

Pin7 |

ALARMA_SALIDA |

Pin20 |

GND |

|

Pin8 |

SDMMC0_PWREN |

Pin21 |

VCC_12V |

|

Pin9 |

SDMMC0_D2 |

Pin22 |

VCC_12V |

|

Pin10 |

USB_PWREN |

Pin23 |

POE45 |

|

Pin11 |

SDMMC0_CMD |

Pin24 |

POE78 |

|

Pin12 |

GND |

Pin25 |

POE36 |

|

Pin13 |

SDMMC0_D1 |

Pin26 |

POE12 |

preguntas frecuentes

- La dirección IP predeterminada de la cámara es 192.168.31.88.

- Si conecta nuestra muestra por cable de red con su computadora, puedes usar esto 169.254.95.254 modificar parámetro.

Usuario: administración

Contraseña: administración

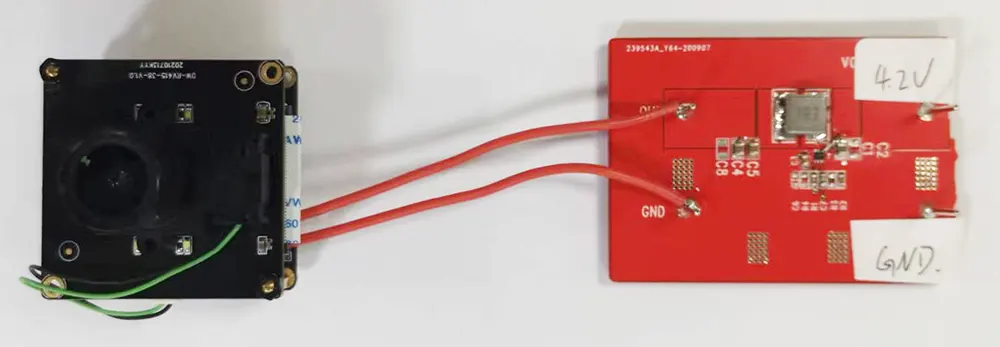

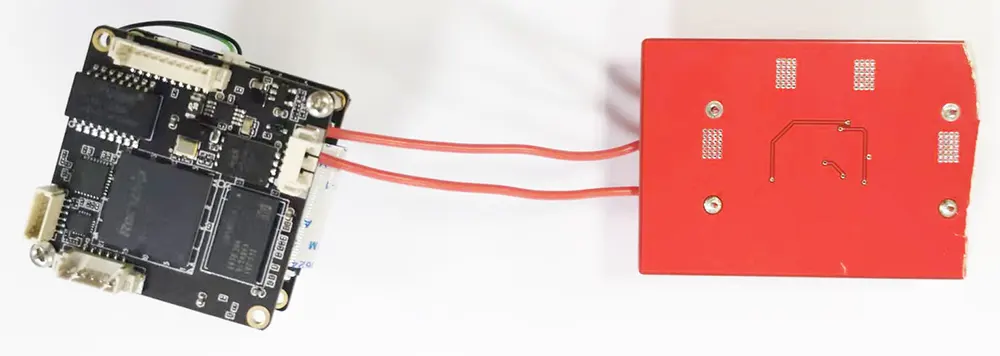

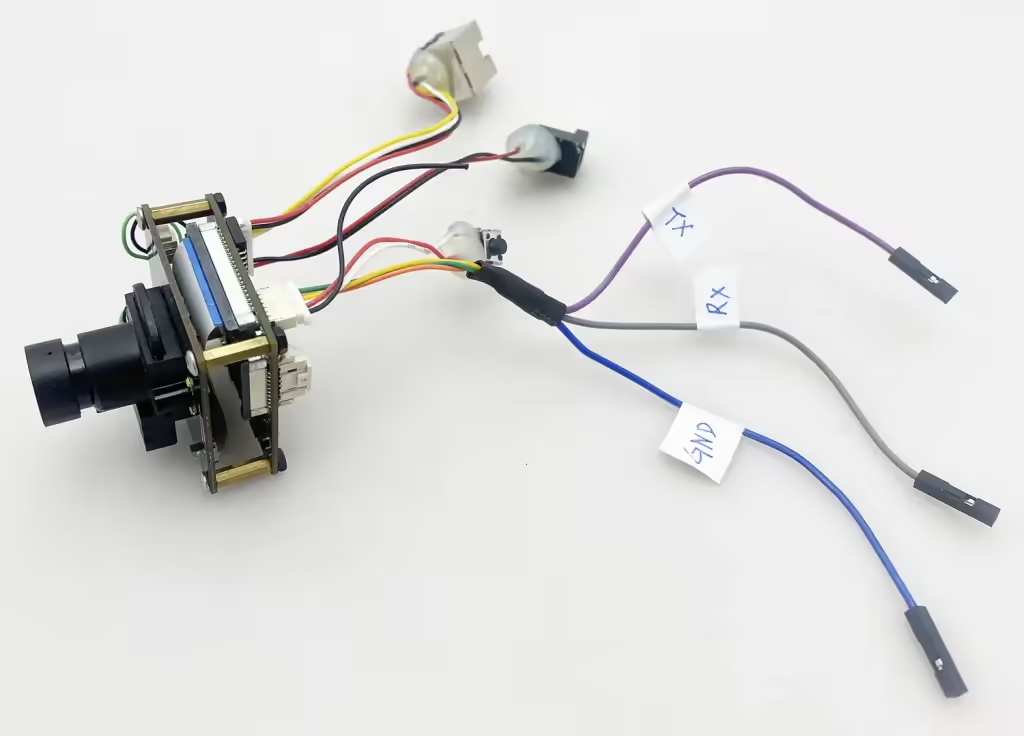

Por favor, compruebe la imagen de abajo, Solo una corta conexión pronto P2 y P3 y activará el inicio. entonces puedes aflojar la conexión.

Sí, vamos a modificar de acuerdo a su requerimiento.

Necesitas 4.2 voltios, tenemos que reemplazar el IC de potencia, pero los pines y los circuitos periféricos de los dos circuitos integrados de potencia son diferentes. Nuestros ingenieros han probado muchos métodos pero no pueden modificar directamente la placa original., así que solo podemos usar esto temporalmente. en el tablero rojo, se adjunta un IC de fuente de alimentación para cumplir con sus requisitos.

https://youtu.be/toh4bY1kTuw

El tamaño de la placa pcba es de 38x38 mm.

El diámetro de cuatro orificios es de 2 mm.

La distancia de dos orificios es de 34 mm.

usuario: raíz

clave: astilla de roca

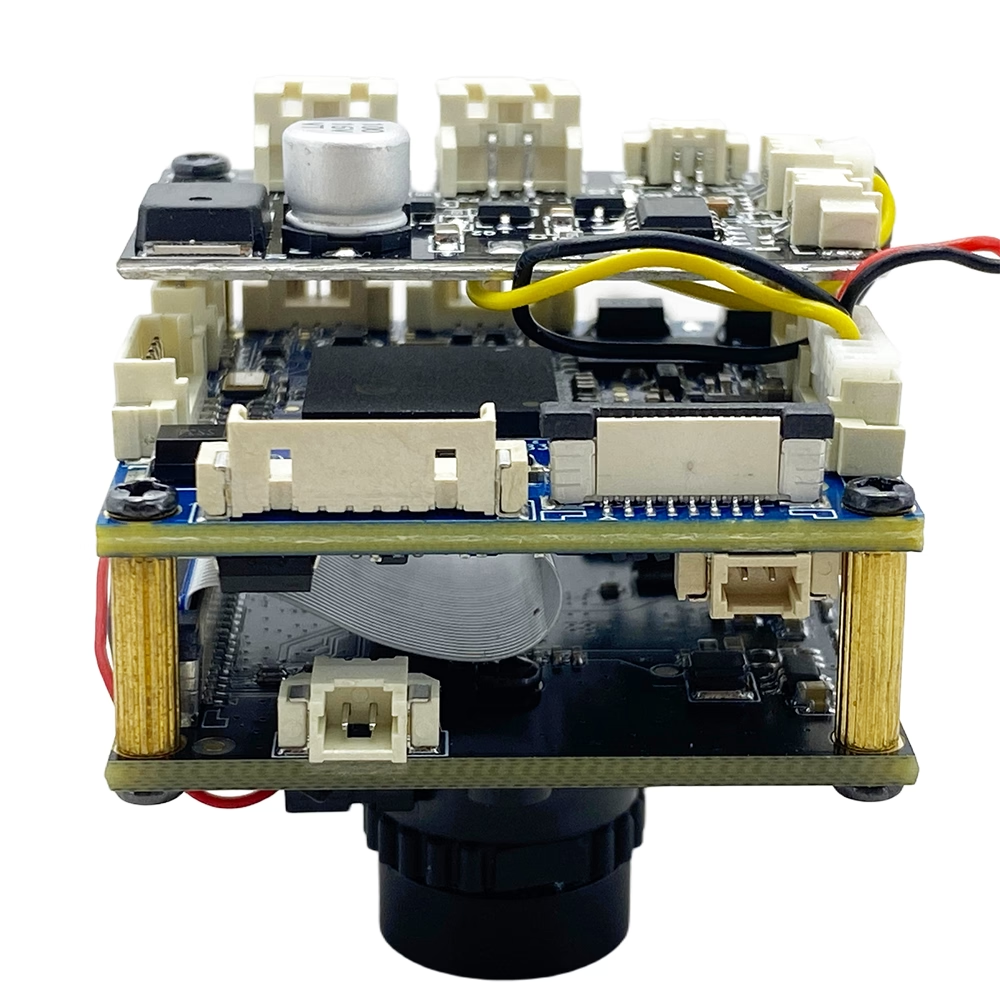

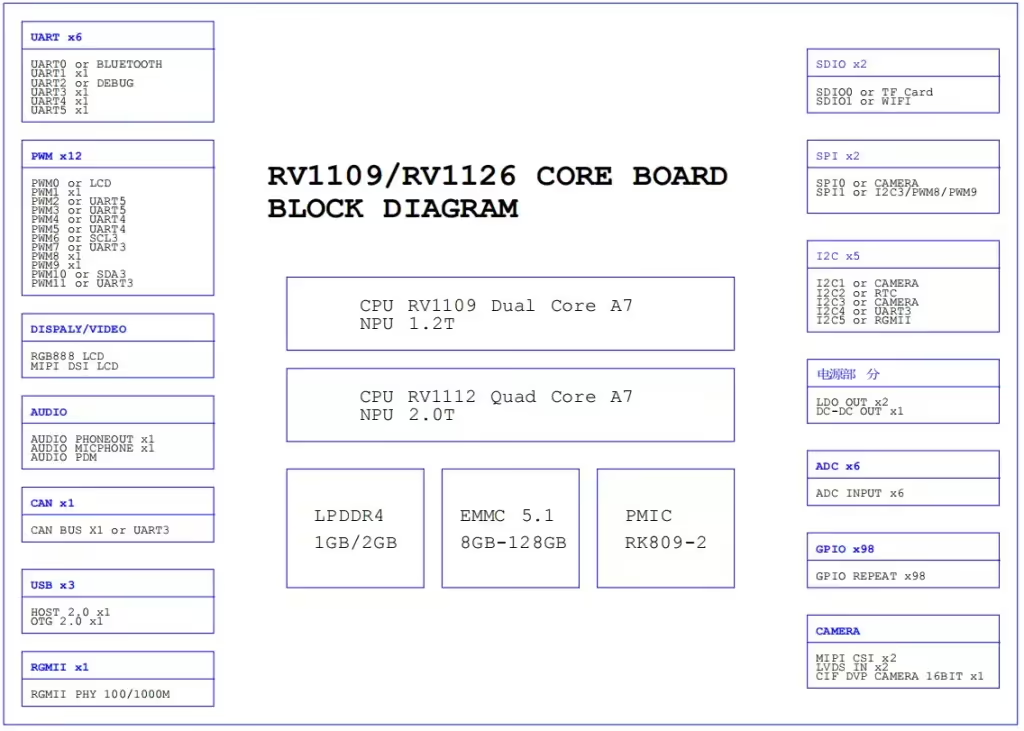

Requisitos de hardware

1. Módulo de cámara Sony IMX415 (Módulo de cámara con interfaz MIP)

2. Cable de cinta MiPi (cable para conectar la cámara con PCB SBC)

3. Tarjeta de cámara principal RV1126

4. Arnés de cable (Mazo de cables con USB POE, Poder, y conector de audio RCA)

5. POE Bcard para SBC (Placa adaptadora POE para PCB SBC)

6. Adaptador de corriente (Fuente de alimentación de CC para la unidad de cámara)

7. Programación USB / cable de depuración (Beneficios según objetivos) (USB separado, Cable tipo OTG para programar y depurar SBC)

8. LED / tableros de infrarrojos (Placa IR y LED para montaje de cámara)

9. MIC

10. Samsung eMMC con memoria basada en SLC/MLC

11. Memoria RAM Samsung

12. red realtek: con soporte PoE

13. Batería RTC

Sí, estamos felices de desarrollar una nueva función para satisfacer su demanda.

Sí, nuestra placa de desarrollo RV1126 tiene soporte adicional para lectores de tarjetas TF.

OK. Te enviaré por correo electrónico.

Responder: El ingeniero respondió que su herramienta de desarrollo Rockchip RV1126 solo es para Windows.

Pregunta: Tendremos acceso root? Si es root podemos instalar cualquiera de nuestros programas. (incl. Linux)

Responder: Sí.

Pregunta: ¿Puedo pedirle un enlace a los repositorios para descargar el SDK?, (herramientas de desarrollo)?

Responder: Sí, RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=compartir

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=compartir

Pregunta: Necesitamos un compuesto (CVBS) vídeo en su módulo Rockchip RV1126. ¿Puedes apoyarlo?? Solo agregue DSI al chip convertidor de video analógico.

Responder: ¿Necesita una placa de desarrollo RV1126 para admitir un compuesto? (CVBS) Entrada para la cámara CVBS normal.?

En caso afirmativo, por favor revise el siguiente enlace, lo desarrollamos para otro cliente.

RV1126 personalizado para cámara web USB o CVBS.

También podemos desarrollar la otra función si la necesita..

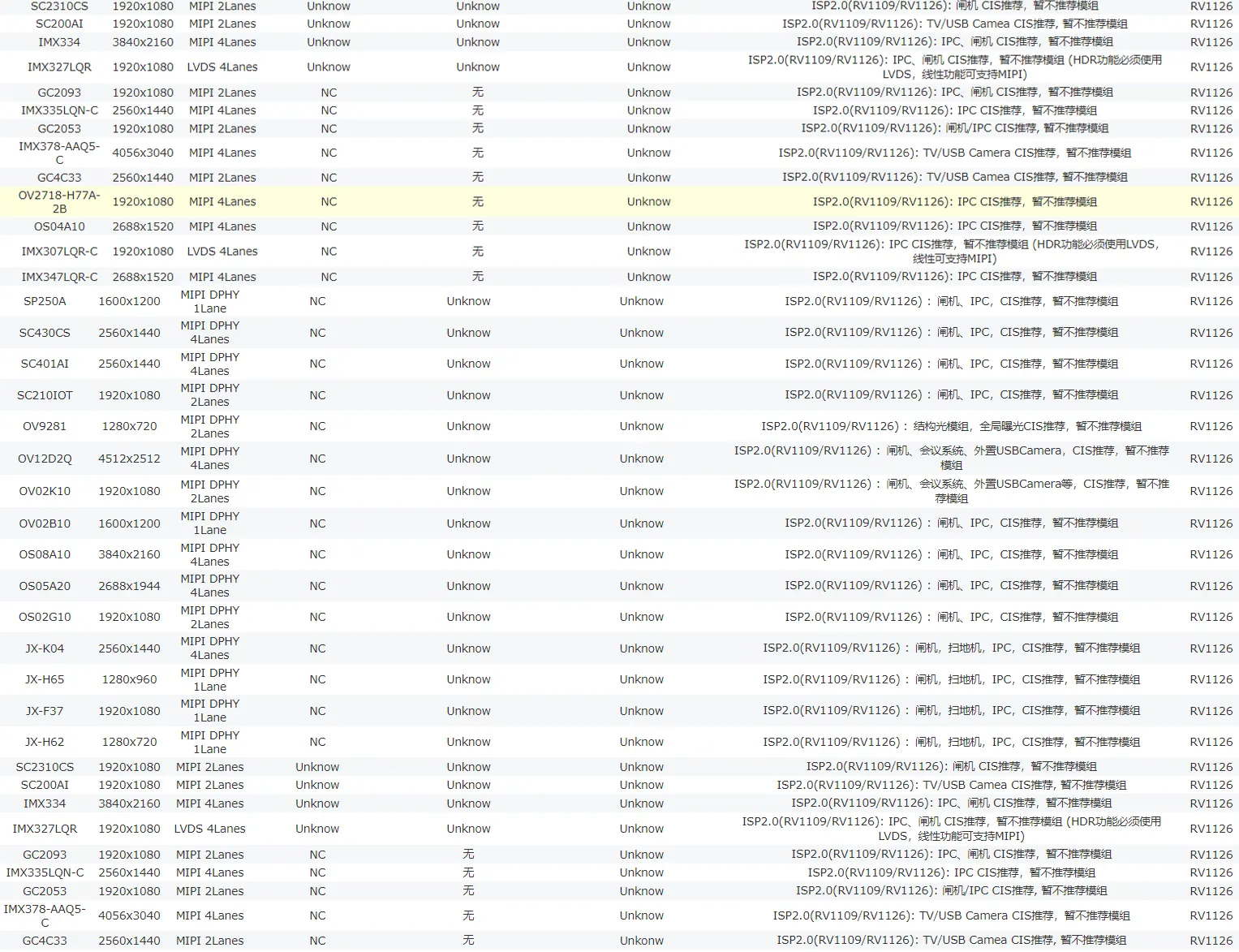

Pregunta 1: ¿Qué controladores de cámara son compatibles con el SDK??

Responder 1:

Pregunta 2: Qué controladores de pantalla MIPI DSI son compatibles con el SDK?

Responder 2: MIPI DSI se depura según la pantalla específica. Por favor, compruebe la imagen de abajo.

Disponemos de otra tabla opcional.; déjanos saber si lo requieres.

1.1 Visión de conjunto

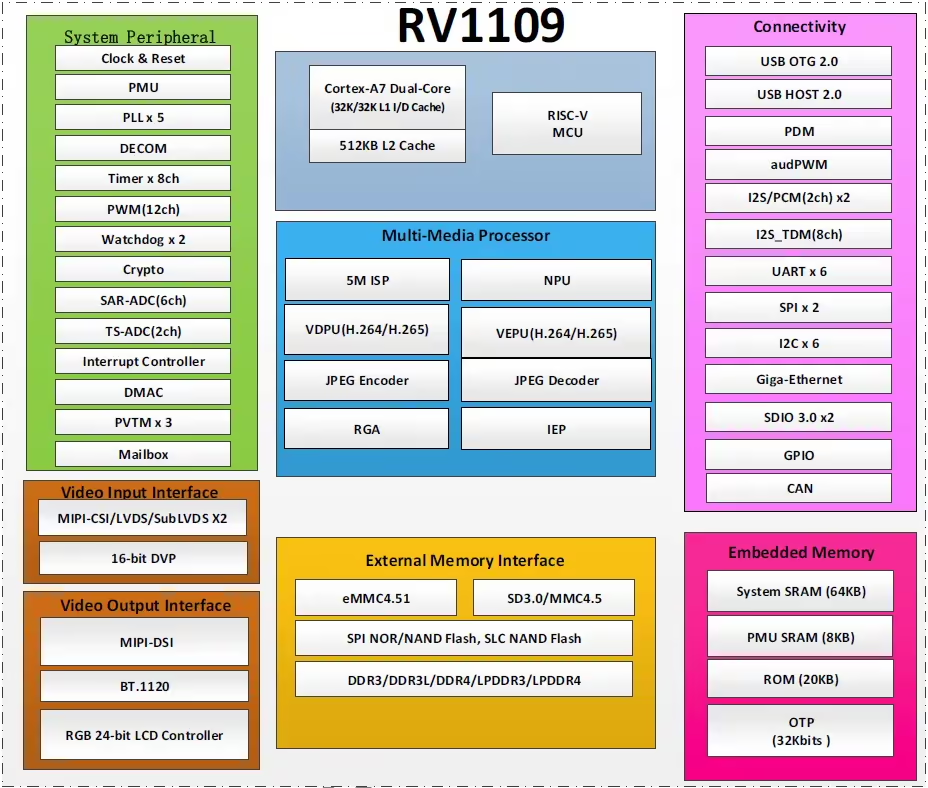

RV1126 es un SoC de procesador de visión de alto rendimiento para IPC/CVR, especialmente para aplicaciones relacionadas con la IA. Se basa en un núcleo ARM Cortex-A7 de 32 bits de cuatro núcleos que integra NEON y FPU. Hay un caché I de 32 KB y un caché D de 32 KB para cada núcleo y un caché L2 unificado de 512 KB. La NPU integrada es compatible con el funcionamiento híbrido INT8/INT16 y la potencia informática es de hasta 2,0 TOP. en adición, con su fuerte compatibilidad, Los modelos de red basados en una serie de marcos como TensorFlow/MXNet/PyTorch/Caffe se pueden convertir fácilmente.<hermano>

RV1126 también presenta una nueva generación de ISP de 14 megapíxeles totalmente basada en hardware (procesador de señal de imagen) y posprocesador. Implementa una gran cantidad de aceleradores de algoritmos generalmente utilizados en IPC y CVR., como HDR, 3Una funciones (Alabama, DE, AWB), LSC, 3DNR, 2DNR, afilado, desempañar, corrección de ojo de pez, corrección gamma, detección de puntos característicos, etc.. Todos ellos son de procesamiento en tiempo real.. Cooperando con dos MIPI CSI (o LVDS/SubLVDS) y un DVP (BT.601/BT.656/BT.1120) interfaz, los usuarios pueden construir un sistema que reciba datos de video de 3 sensores de cámara simultáneamente.

El codificador de video integrado en RV1126 admite la codificación UHD H.265/H.264. También es compatible con la codificación de transmisión múltiple, hasta una 4Kp30 y una 1080p30 simultáneas. Con la ayuda de esta característica, el video de la cámara puede codificarse con una resolución más alta y almacenarse en la memoria local y transferirse a otro video de menor resolución al almacenamiento en la nube al mismo tiempo. El decodificador de video H.264/H.265 en RV1126 admite 4Kp30 para H.264 y H.265.

Además del anterior bloque multimedia de alto rendimiento, RV1126 también contiene audio enriquecido, memoria, y otras interfaces periféricas como I2C, SPI, PWM, y así. Estos pueden ayudar a los usuarios a agregar más sensores u otros periféricos en todo el sistema para mejorar la flexibilidad y la capacidad de expansión..

RV1126 tiene DRAM externa de alto rendimiento (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133) capaz de soportar anchos de banda de memoria exigentes.

1.2 Caracteristicas

Las funciones enumeradas a continuación, que pueden o no estar presentes en un producto real, pueden estar sujetas a los requisitos de licencia de terceros.. Comuníquese con Rockchip para conocer las configuraciones de características del producto y los requisitos de licencia..

1.2.1 Procesador de aplicaciones

Cortex-A7 de cuatro núcleos

Implementación completa del conjunto de instrucciones de la arquitectura ARM v7-A, ARM neón avanzado SIMD

Neon y FPU integrados por separado

32KB L1 I-Cache y 32KB L1 D-cache por CPU Cortex-A7

Caché unificado L2 de 512 KB para Quad-Core Cortex-A7

Tecnología TrustZone compatible

Dominios de energía separados para el sistema central de la CPU para admitir el interruptor de alimentación interno y el encendido/apagado externo según el escenario de aplicación diferente

PD_CPU0: 1San Cortex-A7 + Neón + FPU + Caché de I/D L1

PD_CPU1: 2y Cortex-A7 + Neón + FPU + Caché de I/D L1

PD_CPU2: 3Tercera Cortex-A7 + Neón + FPU + Caché de I/D L1

PD_CPU3: 4Cortex-A7 + Neón + FPU + Caché de I/D L1

Un dominio de voltaje aislado para admitir DVFS

1.2.2 Interfaz de entrada de vídeo

Interfaz y procesador de entrada de video

Dos interfaces MIPI CSI/ LVDS/SubLVDS, 4 carriles cada uno, La velocidad de datos máxima de MIPI CSI es de 2,5 Gbps/carril, La velocidad de datos máxima de LVDS/SublVDS es de 1 Gbps/carril

En la interfaz DVP estándar de 8/10/12/16 bits, datos de entrada de hasta 150 MHz

Admite interfaces VI BT.601/BT.656 y BT.1120

Admite la polaridad de pixel_clk、sincronización、vsync configurable

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

ISP

La resolución máxima es de 14 megapíxeles(4416×3312)

Entrada DVP: UIT-R BT.601/656/1120 con raw8/raw10/raw12/raw16, YUV422

Entrada MIPI: Línea de datos RX x1/x2/x4, crudo8/crudo10/crudo12, YUV422

3A: incluir AE/Histograma, DE, Salida de estadísticas AWB

FPN: Eliminación de ruido de patrón fijo

CLB: Corrección de nivel de negro

DPCC: Corrección de clúster de píxeles defectuosos estáticos/dinámicos

LSC: Corrección de sombreado de lentes

Bayer NO: Eliminación de ruido sin procesar de Bayer, 2DNR

HDR: 3-/2-Combinación de fotogramas en rango dinámico alto

TMO: 3-/2-Asignación de tonos de video de combinación de cuadros

WDR: Mapeo de tonos de rango dinámico amplio de un cuadro

Debayer: Demosaico adaptativo avanzado con corrección de aberración cromática

MCP/MCS: Matriz de corrección de color; RGB2YUV, etc..

Gama: Corrección de salida gamma

Quitar neblina/Mejorar: Eliminación automática de neblina y mejora de bordes

3DLUT: 3Paleta de colores D-Lut para el cliente

LDCH: Distorsión de la lente en la dirección horizontal

Escala de salida*3: nivel de reducción de soporte * 3(W0&es;3264; W1&es;1280; W2&es;1280)

Escala de salida*2: Nivel de reducción de soporte * 2(W0&es;1920; W1&es;1920)

Salida (FBC): Admite YUV422/420 con compresión de búfer de cuadro

3DNR: Reducción de ruido temporal avanzada en YUV

2DNR: Reducción avanzada de ruido espacial en YUV

Afilado: Nitidez de imagen &erio; Mejora de bordes en YUV

ORBE: BREVE Orientado Rápido y Girado, un método de detección de puntos característicos

FEC: mayor distorsión de lente y corrección de ojo de pez

CCG: Compresión de la gama de colores, Convertir rango completo/rango límite YUV

1.2.3 Códec de vídeo

Decodificador de vídeo

Decodificación en tiempo real de H.264 y H.265

Perfil Main y Main10 para H.265, hasta el nivel 5.0 y 4096×2304@30fps

Línea base, principal, alto, alto10 y alto 4:2:2(sin MBAFF), hasta el nivel 5.1 y 4096×2304@30fps

Codificador de vídeo

Codificación de video UHD H.265/H.264 en tiempo real

Marcos I-/P y referencia SmartP.

Modos de control de velocidad de cinco bits (CBR, VBR, arreglarqp, AVBR, y QpMap)

Hasta 100 Tasa de bits de salida Mbit/s

Apoyar el retorno de la inversión(sin límite) codificacion;

Perfil alto para H.264, hasta el nivel 5.1 y 4096×2304@30fps

Perfil principal para H.265, hasta el nivel 5.0 y 4096×2304@30fps

Admite codificación de flujo múltiple

3840 x2160 a 30 fps + 1080codificación p@30 fps

3840 codificación x2160@30 + 3840 x 2160 @ 30 fps decodificación

Formato de datos de entrada:

YCbCr 4:2:0 plano

YCbCr 4:2:0 semiplano

YCbYCr 4:2:2

CbyCrY 4:2:2 intercalado

RGB444 y BGR444

RGB555 y BGR555

RGB565 y BGR565

RGB888 y BRG888

RGB101010 y BRG101010

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

Un dominio de voltaje aislado para admitir DVFS

1.2.4 CÓDEC JPEG

Codificador JPEG

Línea base (DCT secuencial)

El tamaño del codificador es de 96×96 a 8192×8192(67megapíxeles)

Hasta 90 millones de píxeles por segundo

Decodificador JPEG

El tamaño del decodificador es de 48×48 a 8176×8176(66.8megapíxeles)

Hasta 76 millones de píxeles por segundo

1.2.5 Unidad de Procesos Neurales

Motor de aceleración de red neuronal con rendimiento de procesamiento de hasta 2.0 PARTES SUPERIORES

Soporte entero 8, entero 16 operación de convolución

Admite marcos de aprendizaje profundo: TensorFlow, TF-lite, Pytorch, café, ONNX, MXNet, Difícil, red oscura

Compatibilidad con la API de OpenVX

Un dominio de voltaje aislado para admitir DVFS

1.2.6 Organización de la memoria

Memoria interna en chip

BootRom

SYSTEM_SRAM en el dominio de voltaje de VD_LOGIC

PMU_SRAM en el dominio de voltaje de VD_PMU para aplicaciones de baja potencia

Memoria externa fuera del chip

DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133①

Destello SPI

eMMC

Tarjeta SD

Flash Nand asíncrono

1.2.7 Memoria interna

BootRom interno

Admite el arranque del sistema desde el siguiente dispositivo:

Interfaz flash FSPI

Interfaz eMMC

Interfaz SDMMC

Interfaz asíncrona Nand

Admite la descarga del código del sistema mediante la siguiente interfaz:

Interfaz USB OTG (modo de dispositivo)

SISTEMA_SRAM

Tamaño: 64KB

PMU_SRAM

Tamaño: 8KB

1.2.8 Memoria externa o dispositivo de almacenamiento

Interfaz de memoria dinámica (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133)

Compatible con los estándares JEDEC

Compatible con DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133

Admite ancho de datos de 32 bits, 2 rangos (selecciones de chip), espacio de direccionamiento máximo de 4 GB por rango, el espacio de direccionamiento total es de 4GB (máx)

Modos de bajo consumo, como apagado y actualización automática para SDRAM

Interfaz eMMC

Compatible con la interfaz iNAND estándar

Compatible con la especificación eMMC 4.51

Admite tres anchos de bus de datos: 1-poco, 4-bit u 8 bits

Admite hasta HS200; pero no es compatible con CMD Queue

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

Interfaz SD/MMC

Compatible con SD3.0, MMC versión 4.51

El ancho del bus de datos es de 4 bits

Interfaz flash serie flexible(FSPI)

Admite la transferencia de datos desde/hacia un dispositivo flash en serie

Apoyo x1, x2, modo de bits de datos x4

Apoyo 2 selección de fichas

Interfaz Flash Nand

Soporte asíncrono nand flash

El ancho del bus de datos es de 8 bits

Apoyo 1 selección de chips

Soporte LBA nand flash

Hasta 16 bits/1 KB de hardware ECC

Admite temporización de interfaz configurable

1.2.9 Componente del sistema

MCU RISC-V

Núcleo de microcontrolador de 32 bits con RISC -V ISA

Arquitectura Harvard, instrucción separada, y memorias de datos

El conjunto de instrucciones es RV32I con extensiones M y C

Controlador de interrupción programable integrado (IPIC), todos 123 Las líneas IRQ conectadas a GIC para Cortex-A7 también se conectan a RISC –V MCU

Controlador de depuración integrado con interfaz JTAG

CRU (reloj &erio; unidad de reinicio)

Compatibilidad con control de sincronización de reloj para componentes individuales

Un oscilador con entrada de reloj de 24MHz

Admite control global de reinicio suave para todo el chip, también soft-reset individual para cada componente

UGP (unidad de administración de energía)

Apoyo 5 dominios de voltaje separados VD_CORE/VD_LOGIC/VD_PMU/VD_NPU/VD_VEPU

Apoyo 14 dominios de poder separados, que puede ser encendido/apagado por software basado en diferentes escenas de aplicación

Múltiples modos de trabajo configurables para ahorrar energía mediante diferentes frecuencias o control automático de sincronización de reloj o control de encendido/apagado del dominio de energía

Temporizador

Apoyo 6 64temporizadores de bits con operación basada en interrupciones para aplicaciones no seguras

Apoyo 2 64temporizadores de bits con operación basada en interrupciones para aplicaciones seguras

Soporta dos modos de operación: conteo libre y definido por el usuario

Estado de trabajo del temporizador de soporte comprobable

PWM

Apoyo 12 PWM en chip (PWM0~PWM11) con la operación basada en interrupciones

La operación preescalada programable al reloj del bus y luego escalada aún más

Temporizador/contador de 32 bits integrado

Admite modo de captura

Admite modo continuo o modo de una sola toma

Proporciona modo de referencia y genera varias formas de onda de ciclo de trabajo

Optimizado para aplicación IR para PWM3, PWM7, y PWM11

Vigilancia

Contador de vigilancia de 32 bits

El contador cuenta hacia atrás desde un valor preestablecido hasta 0 para indicar la ocurrencia de un tiempo de espera

WDT puede realizar dos tipos de operaciones cuando se agota el tiempo de espera:

Generar un reinicio del sistema

Primero, genere una interrupción y, si la rutina de servicio no la elimina antes de que ocurra un segundo tiempo de espera, genere un reinicio del sistema

Duración del pulso de reinicio programable

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

Totalmente 16 rangos definidos del período de tiempo de espera principal

Un Watchdog para aplicaciones no seguras

Un Watchdog para una aplicación segura

Controlador de interrupciones

Apoyo 128 Entrada de fuentes de interrupción SPI de diferentes componentes

Apoyo 16 interrupciones activadas por software

Dos salidas de interrupción (nFIQ y nIRQ) por separado para cada Cortex-A7, ambos son sensibles a bajo nivel

Admite diferentes prioridades de interrupción para cada fuente de interrupción, y siempre son programables por software

DMAC

DMA basado en programación de microcódigo

Se admite la función DMA de lista enlazada para completar la transferencia de dispersión y recopilación

Admite tipos de transferencia de datos con memoria a memoria, memoria a periférico, periférico a memoria

Señala la ocurrencia de varios eventos DMA usando las señales de salida de interrupción

Un controlador DMA integrado para el sistema

Características de DMAC:

Soporte 8 canales

27 solicitudes de hardware de periféricos

2 interrumpe la salida

Admite tecnología TrustZone y estado seguro programable para cada canal DMA

Sistema Seguro

Motor de cifrado

Admite cifrado SM2/SM3/SM4

Soporte SHA-1, SHA-256/224, SHA-512/384, y MD5 con relleno de hardware

Elemento de la lista de enlaces de soporte (LLI) transferencia DMA

Admite cifrado AES-128 AES-256 &erio; descifrar cifrado

Admite el modo AES ECB/CBC/OFB/CFB/CTR/CTS/XTS

Soporte DES &erio; cifrar TDES &erio; descifrar cifrado

Admite el modo DES/TDES ECB/CBC/OFB/CFB

Soporte hasta 4096 bits Operaciones matemáticas PKA para RSA/ECC

Admite una configuración de hasta 8 canales

Soporta hasta 256 bits de salida TRNG

Admite codificación de datos para todos los tipos de DDR

Admite OTP seguro

Admite depuración segura

Soporta sistema operativo seguro

Buzón

Un buzón en SoC para dar servicio a la comunicación de MCU A7 y RISC-V

Admite cuatro elementos de buzón por buzón, cada elemento incluye una palabra de datos, registro de una palabra de comando, y un bit de bandera que puede representar una interrupción

Proporcionar 32 registros de bloqueo para que el software los use para indicar si el buzón está ocupado

NIÑOS

Soporte para descomprimir archivos GZIP

Soporte para descomprimir archivos LZ4, incluyendo la estructura general del formato LZ4 Frame y el formato Legacy Frame.

Soporte para descomprimir datos en formato Deflate

Soporte para descomprimir datos en formato ZLIB

Soporta interrupción completa y salida de interrupción de error

Admite verificación Hash32 en el proceso de descompresión LZ4

Admite la función de tamaño límite de los datos descomprimidos para evitar que la memoria se destruya maliciosamente durante el proceso de descompresión

Software de soporte para detener el proceso de descompresión

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

1.2.10 Motor de gráficos

Motor de gráficos 2D (RGA):

Formatos de origen:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 plano, YUV420 semiplano

YUV422 plano, YUV422 semiplano

YUV de 10 bits para YUV420/422 semiplano

BPP8, BPP4, BPP2, BPP1

Formatos de destino:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 plano, YUV420 semiplano

YUV422 plano, YUV422 semiplano

Conversión de formato de píxel, BT.601/BT.709

Resolución máxima: 8192×8192 fuente, 4096×4096 destino

BitBlt

Dos fuentes BitBLT:

A+B=B solo BitBLT, Un soporte gira y escala cuando B está fijo

A+B=C segunda fuente (segundo) tiene el mismo atributo que (do) más función de rotación

Relleno de color con relleno degradado, y relleno de patrón

Estiramiento y contracción de alto rendimiento

Expansión monocromática para representación de texto

Nuevo alfa completo por píxel (color/canal alfa por separado)

Modos de fusión alfa, incluido Java 2 Reglas de mezcla de composición de Porter-Duff, clave de croma, máscara de patrón, desvanecimiento

Operación de interpolación

0, 90, 180, 270-rotación de grados

espejo x, y-espejo, y operación de rotación

Procesador de mejora de imagen (PEI):

Formato de imagen

Datos de entrada: YUV420/YUV422, semiplano/plano, cambio de UV

Datos de salida: YUV420/YUV422, semiplano, cambio de UV, Modo mosaico

Conversión de muestreo descendente YUV de 422 a 420

Resolución máxima para imagen dinámica de hasta 1920 × 1080

Desentrelazado

1.2.11 Interfaz de pantalla

Uno hasta 24 Interfaz de salida de video paralelo RGB de bits

Una interfaz de salida de video BT.1120

Una interfaz MIPI DSI de 4 carriles, hasta 1 Gbps por carril

Hasta 1080p@60fps

1.2.12 Procesador de salida de video (GTC)

Hasta 1920×1080 @60fps

Múltiples capas

Capa de fondo

Capa Win0

Capa Win2

Formato de entrada: RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444

1/8 a 8 motor de escalamiento hacia abajo y escalamiento hacia arriba

Admite visualización virtual

256 mezcla de nivel alfa (soporte alfa premultiplicado)

Tecla de color de transparencia

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

RGB2YCbCr (BT.601/BT.709)

Admite varias regiones

Superposición de capa Win0 y capa Win2 intercambiable

Admite superposición de dominios RGB o YUV

BCSH (Brillo, Contraste, Saturación, Ajuste de tono)

BCSH: YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

BCSH: RGB2YCbCr (BT.601/BT.709)

Compatible con ajuste gamma

Compatibilidad con tramado hacia abajo allegro RGB888to666 RGB888to565 &erio; difuminar FRC (configurable) RGB888 a 666

Pantalla en blanco y negro

1.2.13 Interfaz de audio

I2S0 con 8 canales

Hasta 8 canales TX y 8 canales ruta RX

Resolución de audio de 16 bits a 32 bits

Frecuencia de muestreo de hasta 192 KHz

Proporciona modo de trabajo maestro y esclavo, software configurable

Apoyo 3 formatos I2S (normal, justificado a la izquierda, justificado a la derecha)

Apoyo 4 formatos PCM (temprano, tarde1, tarde2, tarde3)

Los modos I2S y PCM no se pueden usar al mismo tiempo

I2S1/I2S2 con 2 canales

Hasta 2 canales para TX y 2 canales ruta RX

Resolución de audio de 16 bits a 32 bits

Frecuencia de muestreo de hasta 192 KHz

Proporciona modo de trabajo maestro y esclavo, software configurable

Apoyo 3 formatos I2S (normal, justificado a la izquierda, justificado a la derecha)

Apoyo 4 formatos PCM (temprano, tarde1, tarde2, tarde3)

I2S y PCM no se pueden usar al mismo tiempo

PDM

Hasta 8 canales

Resolución de audio de 16 bits a 24 bits

Frecuencia de muestreo de hasta 192 KHz

Admite modo de recepción maestro PDM

TDM

Soporta hasta 8 canales para TX y 8 canales para ruta RX

Resolución de audio de 16 bits a 32 bits

Frecuencia de muestreo de hasta 192 KHz

Proporciona modo de trabajo maestro y esclavo, software configurable

Apoyo 3 formatos I2S (normal, justificado a la izquierda, justificado a la derecha)

Apoyo 4 formatos PCM (temprano, tarde1, tarde2, tarde3)

Audio PWM

Admite conversión de formato PCM a PWM

Tasa de muestreo de hasta 16x

Admite interpolación lineal para sobremuestreo 2x/4x/8x/16

Apoyo 8/9/10/11 Salida PWM de canal L/R enmascarable de bits

Códec de audio digital

Admite ADC digital de 3 canales

Admite DAC digital de 2 canales

Admite interfaz I2S/PCM

Admite modo maestro y esclavo I2S/PCM

Admite transmisión de audio de 4 canales en modo I2S

Admite recepción de audio de 2 canales en modo I2S

Admite transmisión o recepción de audio de 2 canales en modo PCM

Admite una resolución de muestra de 16~24 bits tanto para ADC digital como para DAC digital

<estilo de tramo =”color: #ffffff;”>Hoja de datos RV1126 Rev. 1.4</lapso>

Tanto el ADC digital como el DAC digital admiten tres grupos de frecuencias de muestreo. Grupo 0 son 8 khz/16 khz/32 khz/64 khz/128 khz, grupo 1 son 11.025khz/22.05khz/44.1khz/88.2khz/176.4khz y grupo 2 son 12 khz/24 khz/48 khz/96 khz/192 khz

La banda de paso de los filtros ADC digitales es 0.45625*fs

Admite ondulación de banda de paso ADC digital dentro de +/-0.1dB

La banda de parada de los filtros ADC digitales es 0,5*fs

Admite atenuación de banda de parada ADC digital de al menos 60dB

Admite control de volumen tanto para ADC digital como para DAC digital

Soporte de control de nivel automático (ALC)y puerta de ruido para ADC digital

Admite comunicación con códec analógico a través del bus I2C

1.2.14 conectividad

Interfaz SDIO

Compatible con el protocolo SDIO3.0

Anchos de bus de datos de 4 bits

Controlador ethernet GMAC 10/100/1000M

Admite velocidades de transferencia de datos de 10/100/1000 Mbps con las interfaces RGMII

Admite velocidades de transferencia de datos de 10/100 Mbps con las interfaces RMII

Admite operaciones de dúplex completo y semidúplex Admite descarga de segmentación TCP (TSO) y descarga de segmentación UDP (USAR) aceleración de la red<hermano>

USB 2.0 Anfitrión

Compatible con USB 2.0 especificación

Admite alta velocidad(480mbps), a toda velocidad(12mbps) y baja velocidad(1.5mbps) modo

Compatibilidad con la especificación de interfaz de controlador de host mejorada (EHCI), Revisión 1.0

Compatibilidad con la especificación de la interfaz del controlador de host abierto (OHCI), Revisión 1.0a

USB 2.0 OTG

Especificaciones compatibles

Especificación de bus serie universal, Revisión 2.0

Interfaz de controlador de host extensible para bus serie universal (xHCI), Revisión 1.1

Soporte de control/en masa/interrupción/transferencia isócrona

Interfaz SPI

Apoyo 2 Controladores SPI, Admite dos salidas de selección de chip

Soporta modo serial-master y serial-slave, configurable por software

Interfaz I2C

Apoyo 6 interfaces I2C(I2C0-I2C5)

Admite modo de dirección de 7 bits y 10 bits

Frecuencia de reloj programable por software

Los datos en el bus I2C se pueden transferir a velocidades de hasta 100k bits/s en el modo estándar, hasta 400k bits/s en el modo Rápido, o hasta 1m bits/s en Fast-mode Plus

Interfaz UART

Apoyo 6 interfaces UART (UART0-UART5)

Soporte de 5 bits, 6poco, 7poco, y transmisión o recepción de datos en serie de 8 bits

Bits de comunicación asíncrona estándar como inicio, deténgase, y paridad

Admite diferentes relojes de entrada para la operación UART para obtener una velocidad de transmisión de hasta 4 Mbps

Admite el modo de control de flujo automático(excepto UART2)

1.2.15 Otros

Múltiples grupos de GPIO

Todos los GPIO se pueden usar para generar una interrupción

Disparador de nivel de soporte e interrupción de disparador de borde

Admite polaridad configurable de interrupción de activación de nivel

Soporta flanco ascendente configurable, flanco descendente, y tanto la interrupción del disparador de borde

Soporta dirección de tracción configurable (un pull-up débil y un pull-down débil)

<fuerte>Hoja de datos RV1126 Rev. 1.4</fuerte>

Admite fuerza de accionamiento configurable

Sensor de temperatura (TS-ADC)

Admite el modo definido por el usuario y el modo automático

En modo definido por el usuario, start_of_conversion puede ser controlado completamente por software, y también puede ser generado por hardware.

En Modo Automático, la temperatura de alarma(temperatura alta/baja) la interrupción puede ser configurable

En Modo Automático, la temperatura de reinicio del sistema puede ser configurable

Apoyo a 2 canal TS-ADC (utilizado para CPU y NPU respectivamente), los criterios de temperatura de cada canal pueden ser configurables

Rango de temperatura de -40~125 °C y resolución de temperatura de 5 °C

ADC SAR de 12 bits hasta 732 Tasa de muestreo S/s

ADC de aproximación sucesiva (ADC SAR)

Resolución de 10 bits

Frecuencia de muestreo de hasta 1 MS/s

6 canales de entrada de un solo extremo

Fiscalía

El espacio de soporte de 32 Kbit y el espacio de direcciones superior de 4k es una parte no segura.

Admite máscara de palabra de lectura y programa en un modelo seguro

Admite la duración del programa desde 1 a 32 poco

Soporte de operación de lectura de 8 bits solamente

El programa y el estado de lectura se pueden leer

El programa no logra direccionar el registro

Tipo de paquete

FCCSP de 409 pines (cuerpo: 14mm x 14 mm; Tamaño de la bola: 0.3mm; lanzamiento de pelota: 0.65mm)

Notas:

①: DDR3/DDR3L/DDR4/LPDDR3/LPDDR4 no se usa simultáneamente

Descargar

RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=sharing

SDK

https://drive.google.com/file/d/1CCNWHNNVi8FVG6UXNgrMDYsZx3SrpFyr/view?usp=sharing

Ficha de datos

Hoja de datos de RV1126-Vcan1748

RV1126 RV1109 Inicio rápido

Rockchip_RV1126_RV1109_Quick_Start_Linux_EN

Guía para desarrolladores de Rockchip RockX_SDK

Personalización de la placa de desarrollo RV1126

WIFI & Bluetooth

Otra cámara de marca para reemplazar a Sony IMX415

Una entrada de cámara USB, Transfiere la transmisión de video a otra computadora a través del módulo WIFI

opiniones

No hay comentarios aún.