Da der RV1126-Chip nicht mehr hergestellt wird, Als Ersatzlösung empfehlen wir IPC2188.

Für weitere Details klicken Sie bitte auf den Link unten: Erfahren Sie mehr über IPC2188

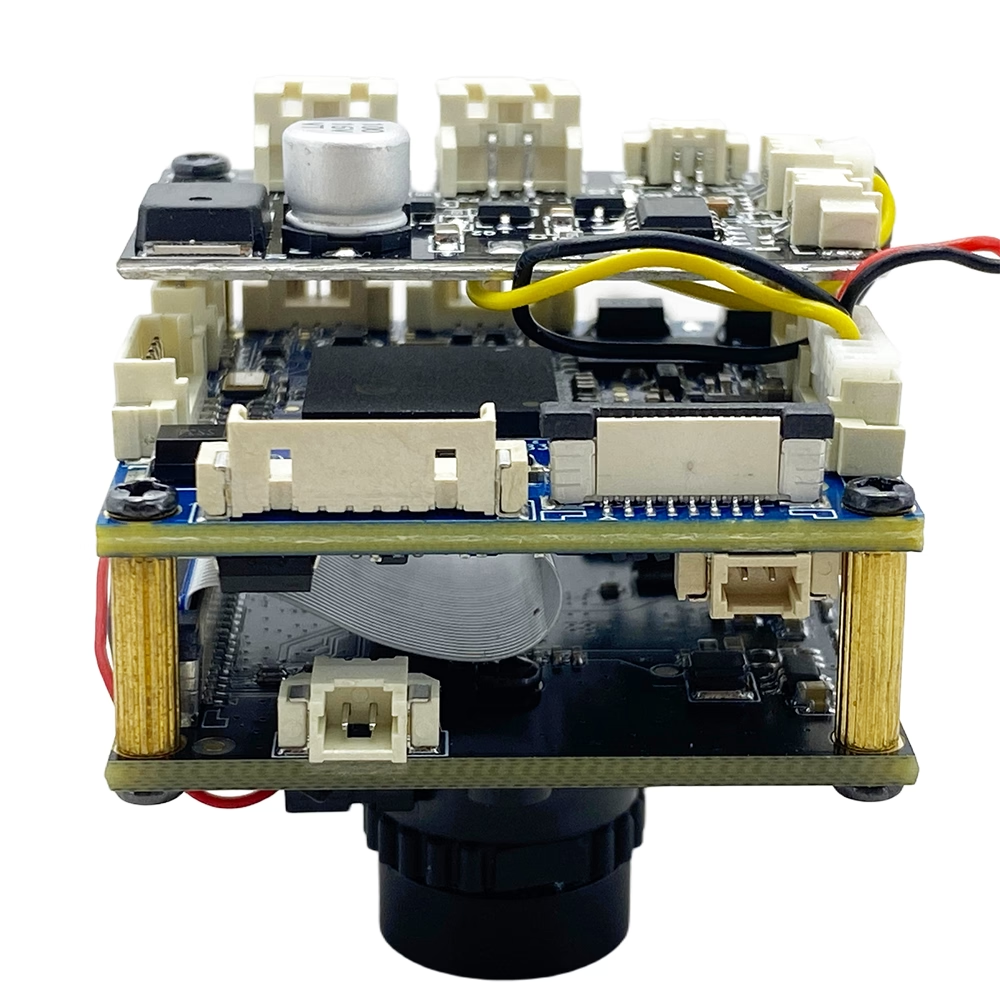

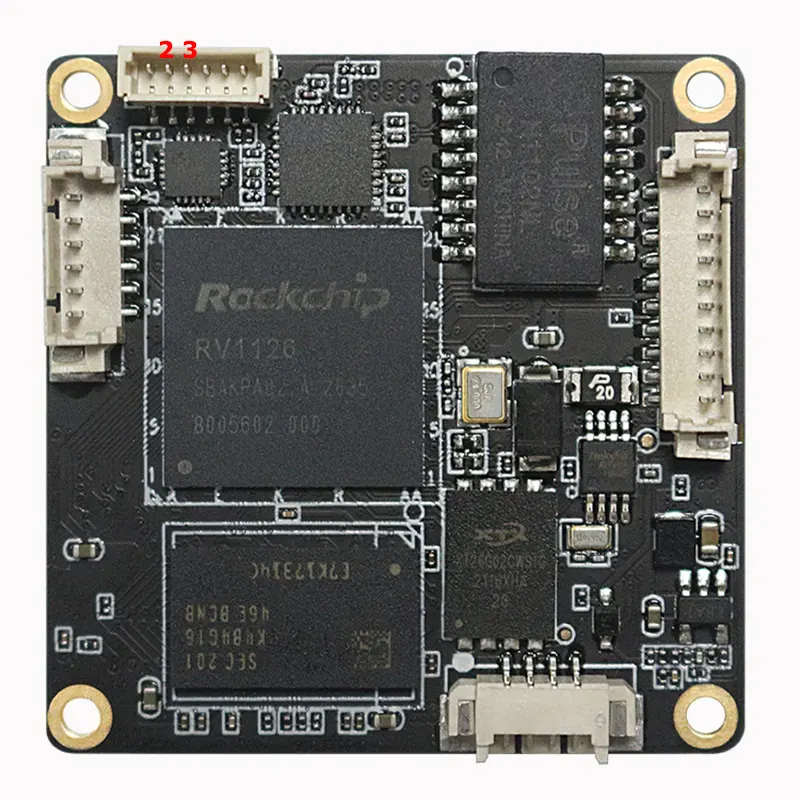

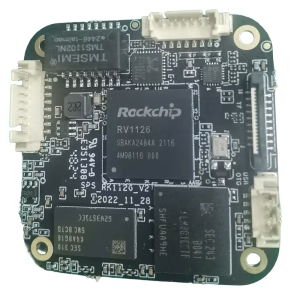

Rockchip RV1126 Development Evaluation Board Kernplatine IPC AI SDK Software Development Kit

Inhaltsverzeichnis

Galerie

Produktanwendungen

Intelligenter IPC, Gesichtserkennungs-Panel-Maschine, Gesichtserfassungskamera, Video-Türklingel, Kein Netzwerk, und No Power Kamera, Express-Handheld, GPS Navigation, Mensch-Maschine-Schnittstelle, Beobachtungs Ausrüstung, Drohnenkapsel, Videokonferenzsystem, etc.

Möchten Sie mit dem Objektivkameramodul Sony IMX415 arbeiten?

Laden Sie das SDK herunter

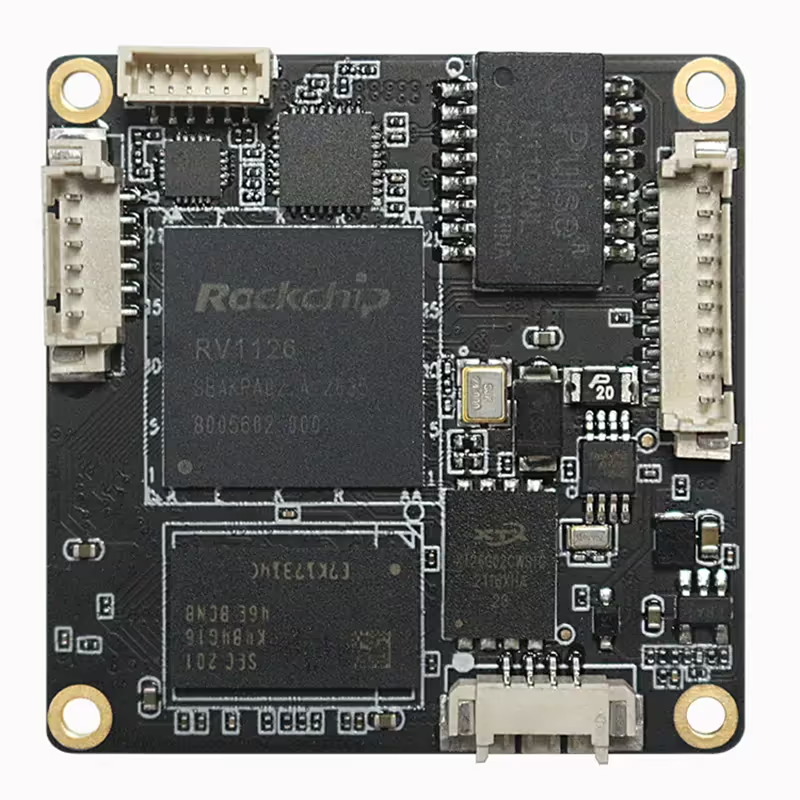

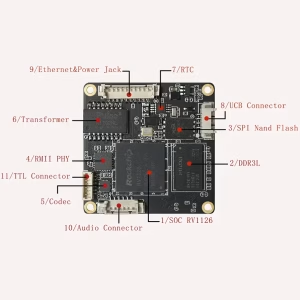

Spezifikation der Vorderansicht

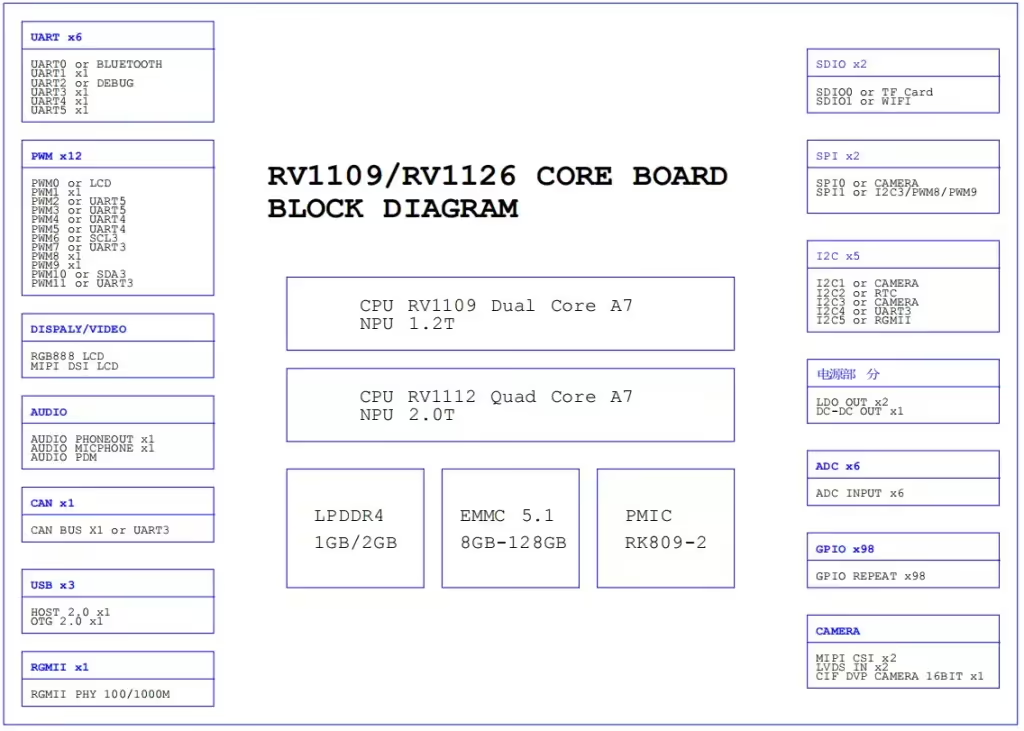

1. SOC RV1126, Pin-zu-Pin-kompatibel mit RV1109;

|

Pin1 |

VCC5V0_OTG |

|

Pin2 |

OTG_DM |

|

Pin3 |

OTG_DP |

|

pin4 |

GND |

9.Ethernet&Stromanschluss

|

Pin1 |

TX+ |

Pin6 |

RX- |

|

Pin2 |

TX- |

Pin7 |

POE78 |

|

Pin3 |

RX+ |

Pin8 |

POE78 |

|

pin4 |

POE45 |

Pin9 |

GND |

|

Pin5 |

POE45 |

Pin10 |

VCC12V_DCIN |

10. Audioanschluss

|

Pin1 |

LED1/PHYAD1 |

|

Pin2 |

LED0 / PHYAD0 |

|

Pin3 |

ZURÜCKSETZEN |

|

pin4 |

MICP |

|

Pin5 |

GND |

|

Pin6 |

LINE_OUT |

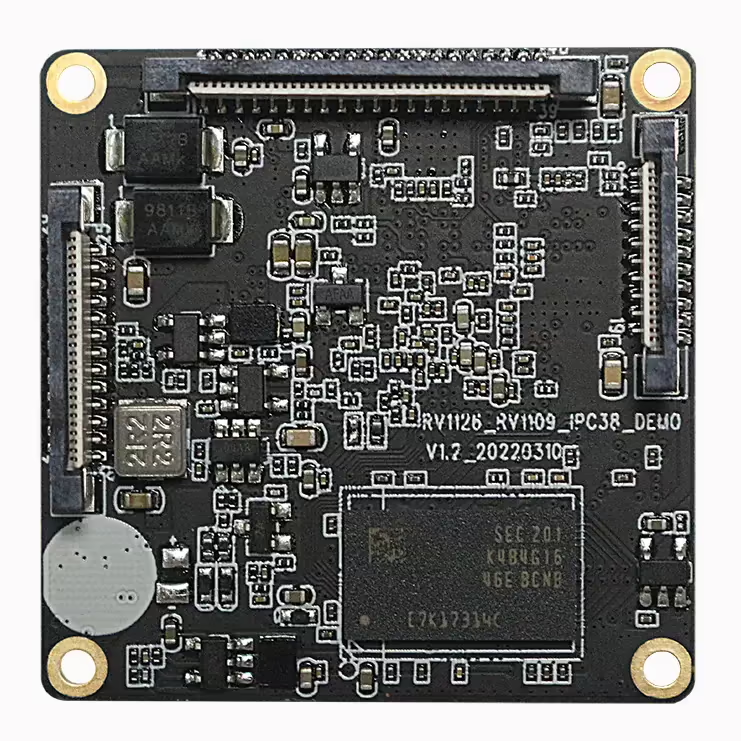

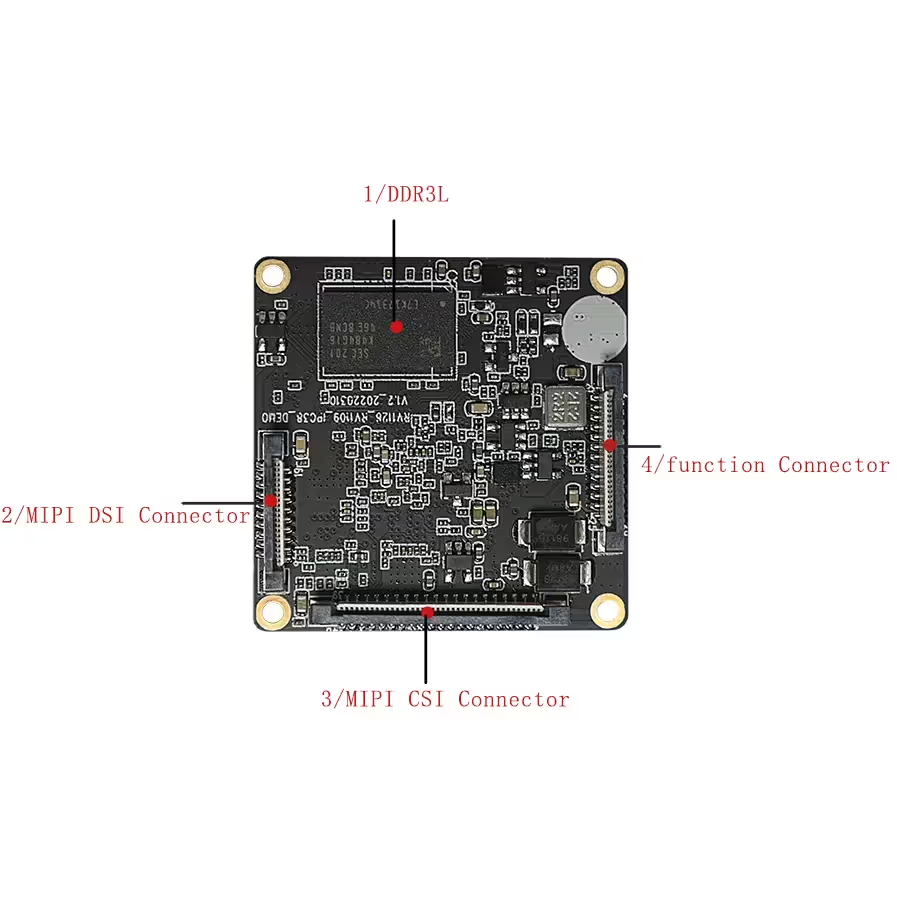

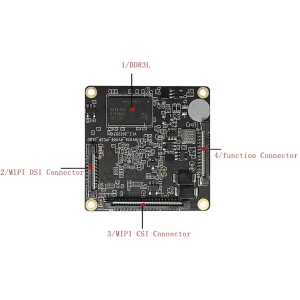

Rückansicht der Spezifikation

1.DDR3L (Samsung K4B4G1646E BCNB)

Ein 4Gbit DDR3 ist auf der Vorder- und Rückseite des gesamten Boards angebracht, mit insgesamt 8G Bits;

2.MIPI-DSI-Anschluss

|

Pin1 |

IRQ |

Pin11 |

MIPI_DSI_D3N |

|

Pin2 |

PWR_EN |

Pin12 |

MIPI_DSI_D3P |

|

Pin3 |

RST |

Pin13 |

MIPI_DSI_D0N |

|

pin4 |

I2C3_SDA |

Pin14 |

MIPI_DSI_D0P |

|

Pin5 |

I2C3_SCL |

Pin15 |

GND |

|

Pin6 |

GND |

Pin16 |

MIPI_DSI_CLKN |

|

Pin7 |

MIPI_DSI_D2P |

Pin17 |

MIPI_DSI_CLKP |

|

Pin8 |

MIPI_DSI_D2N |

Pin18 |

GND |

|

Pin9 |

MIPI_DSI_D1P |

Pin19 |

VCC_12V |

|

Pin10 |

MIPI_DSI_D1N |

Pin20 |

VCC_12V |

3.MIPI-CSI-Anschluss

|

Pin1 |

VCC3V3_SYS |

Pin21 |

MIPI_CSI_RX0_D1N |

|

Pin2 |

VCC3V3_SYS |

Pin22 |

MIPI_CSI_RX0_D0P |

|

Pin3 |

SPI0_CLK |

Pin23 |

MIPI_CSI_RX0_D0N |

|

pin4 |

LED_PWM |

Pin24 |

GND |

|

Pin5 |

SPI0_CS0N |

Pin25 |

MIPI_CSI_CLK0 |

|

Pin6 |

SPI0_MISO |

Pin26 |

GND |

|

Pin7 |

SPI0_MOSI |

Pin27 |

PWM8 |

|

Pin8 |

I2C1_SDA |

Pin28 |

IRC_AIN |

|

Pin9 |

I2C1_SCL |

Pin29 |

PWM11 |

|

Pin10 |

MIPI_RX0_PDN |

Pin30 |

PWM9 |

|

Pin11 |

MIPI_RX0_RST |

Pin31 |

IRC_BIN |

|

Pin12 |

GND |

Pin32 |

ZOOM_EN |

|

Pin13 |

MIPI_CSI_RX0_CLKP |

Pin33 |

PWM10 |

|

Pin14 |

MIPI_CSI_RX0_CLKN |

Pin34 |

P-IRIS_EN |

|

Pin15 |

GND |

Pin35 |

FOCUS_DE |

|

Pin16 |

MIPI_CSI_RX0_D2P |

Pin36 |

ADC_IN |

|

Pin17 |

MIPI_CSI_RX0_D2N |

Pin37 |

GND |

|

Pin18 |

MIPI_CSI_RX0_D3P |

Pin38 |

VCC_1V8 |

|

Pin19 |

MIPI_CSI_RX0_D3N |

Pin39 |

VCC_12V |

|

Pin20 |

MIPI_CSI_RX0_D1P |

Pin40 |

VCC_12V |

4.Funktionskonnektor

|

Pin1 |

HOST_DM |

Pin14 |

SDMMC0_D0 |

|

Pin2 |

HOST_DP |

Pin15 |

SDMMC0_CLK |

|

Pin3 |

GND |

Pin16 |

SDMMC0_D3 |

|

pin4 |

GND |

Pin17 |

RS485_CTL |

|

Pin5 |

ALARM_EIN |

Pin18 |

UART3_RX_485 |

|

Pin6 |

SDMMC0_DET |

Pin19 |

UART3_TX_485 |

|

Pin7 |

ALARM_AUS |

Pin20 |

GND |

|

Pin8 |

SDMMC0_PWREN |

Pin21 |

VCC_12V |

|

Pin9 |

SDMMC0_D2 |

Pin22 |

VCC_12V |

|

Pin10 |

USB_PWREN |

Pin23 |

POE45 |

|

Pin11 |

SDMMC0_CMD |

Pin24 |

POE78 |

|

Pin12 |

GND |

Pin25 |

POE36 |

|

Pin13 |

SDMMC0_D1 |

Pin26 |

POE12 |

Häufig gestellte Fragen

- Die Standard-IP-Adresse der Kamera ist 192.168.31.88.

- wenn Sie unser Muster per Netzkabel mit Ihrem Rechner verbinden, Sie können dies verwenden 169.254.95.254 Parameter zu ändern.

Benutzer: Administrator

Passwort: Administrator

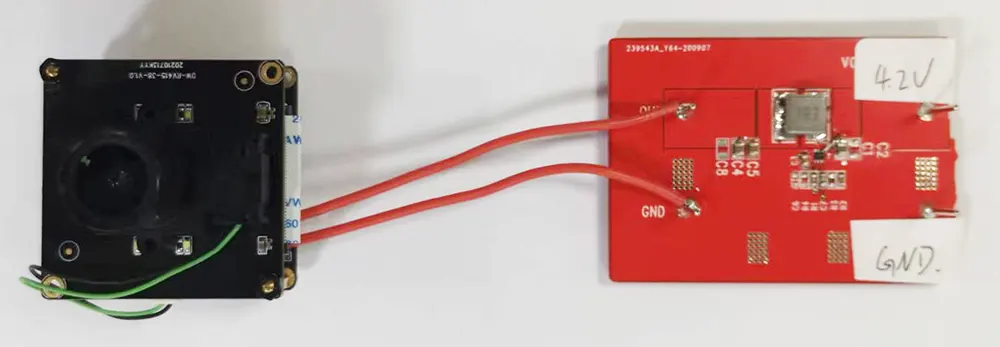

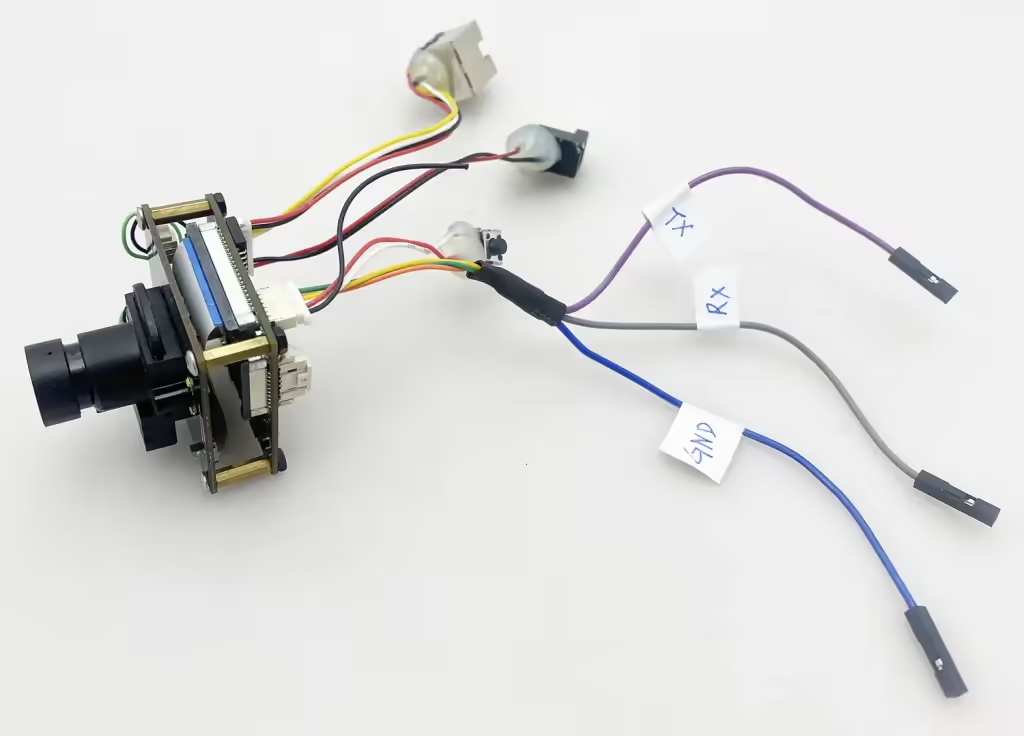

Überprüfen Sie bitte das Bild unten, Gerade eine kurze Verbindung bald P2 und P3 und es wird den Start auslösen. dann kannst du die verbindung lösen.

Ja, wir ändern entsprechend Ihrer Anforderung.

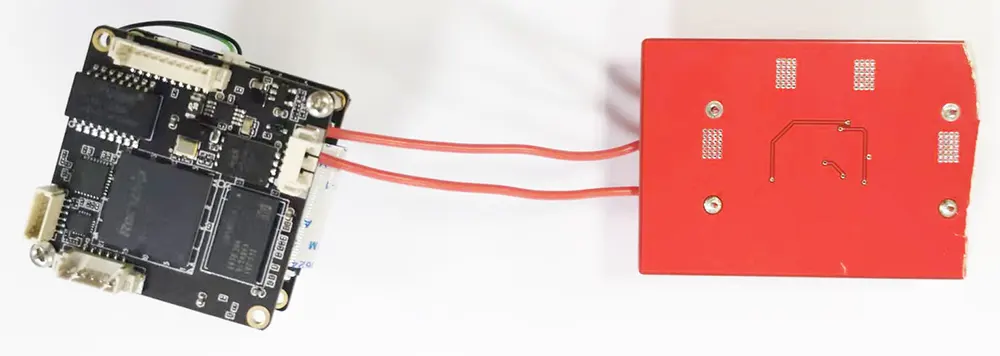

Du brauchst 4.2 Volt, Wir müssen den Leistungs-IC ersetzen, aber die Pins und Peripherieschaltungen der beiden Leistungs-ICs sind unterschiedlich. Unsere Ingenieure haben viele Methoden ausprobiert, können die Originalplatine jedoch nicht direkt modifizieren, Daher können wir dies nur vorübergehend verwenden. Auf der roten Tafel, Ein Netzteil-IC ist beigefügt, um Ihre Anforderungen zu erfüllen.

https://youtu.be/toh4bY1kTuw

Die Abmessungen der Leiterplatte betragen 38 x 38 mm

Der Durchmesser der vier Löcher beträgt 2 mm

Der Abstand zwischen zwei Löchern beträgt 34 mm

Benutzer: Wurzel

Passwort: Steinschlag

Hardware-Anforderungen

1. Sony IMX415 Kameramodul (Kameramodul mit MIP-Schnittstelle)

2. MiPi-Flachbandkabel (Kabel zum Verbinden der Kamera mit der SBC-Leiterplatte)

3. Hauptkamera RV1126 in Richtung

4. Kabelbaum (Kabelbaum mit USB POE, Leistung, und Cinch-Audioanschluss)

5. POE-Bcard für SBC (POE-Adapterplatine für SBC-Leiterplatte)

6. Netzteil (Gleichstromquelle für die Kameraeinheit)

7. USB-Programmierung / Debug-Kabel (OTe) (Separater USB, Kabel vom Typ OTG zum Programmieren und Debuggen von SBC)

8. LED / IR-Boards (IR- und LED-Platine zur Kameramontage)

9. MIC

10. Samsung eMMC mit SLC/MLC-basiertem Speicher

11. Samsung-RAM

12. Realtek-Ethernet: mit PoE-Unterstützung

13. RTC-Batterie

Ja, Wir freuen uns, eine neue Funktion zu entwickeln, um Ihre Anforderungen zu erfüllen.

Ja, Unser RV1126-Entwicklungsboard verfügt über zusätzliche Unterstützung für TF-Kartenleser.

OK. Ich sende Ihnen per E-Mail.

Antworten: Der Ingenieur antwortete, dass sein Entwicklungstool Rockchip RV1126 nur für Windows gedacht sei.

Frage: Wir werden Root-Zugriff haben? Wenn wir root sind, können wir jedes unserer Programme installieren (inkl. Linux)

Antworten: Ja.

Frage: Darf ich Sie um einen Link zu Repositories zum Herunterladen des SDK bitten?, (Entwicklungstools)?

Antworten: Ja, RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=teilen

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=teilen

Frage: Wir brauchen einen Verbund (CVBS) Video auf Ihrem Rockchip RV1126-Modul. Können Sie es unterstützen?? Fügen Sie nur DSI zum analogen Videokonverterchip hinzu.

Antworten: Benötigen Sie eine RV1126-Entwicklungsplatine zur Unterstützung eines Verbundwerkstoffs? (CVBS) Eingang für die normale CVBS-Kamera?

Falls ja, Bitte überprüfen Sie den unten stehenden Link, Wir entwickeln es für einen anderen Kunden.

RV1126 angepasst für USB-Web- oder CVBS-Kamera.

Bei Bedarf können wir auch die andere Funktion entwickeln.

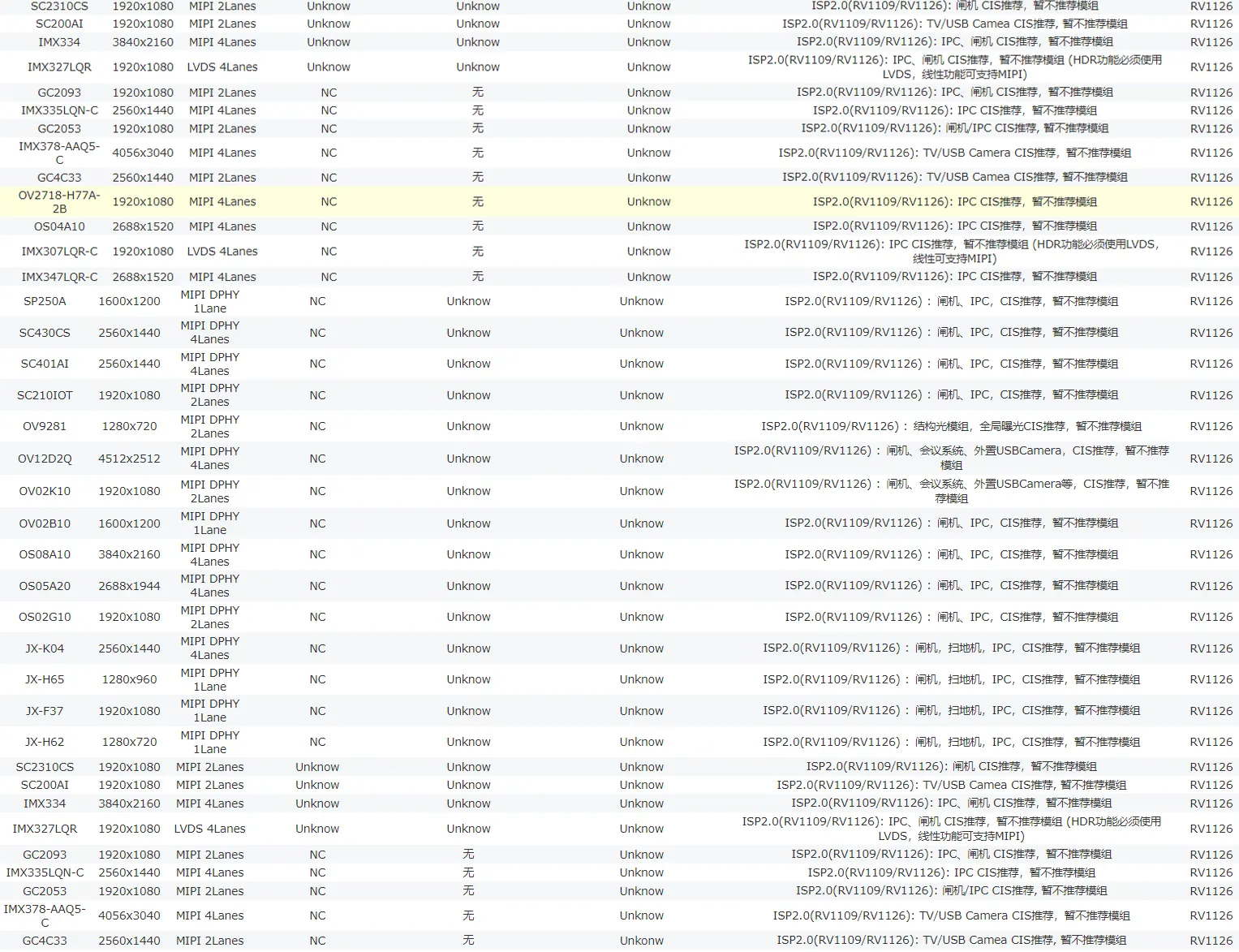

Frage 1: Welche Kameratreiber werden vom SDK unterstützt??

Antworten 1:

Frage 2: Welche MIPI-DSI-Anzeigetreiber werden vom SDK unterstützt??

Antworten 2: MIPI DSI wird basierend auf dem spezifischen Bildschirm debuggt. Überprüfen Sie bitte das Bild unten.

Wir haben eine andere optionale Karte; Lassen Sie uns wissen, ob Sie es benötigen.

1.1 Überblick

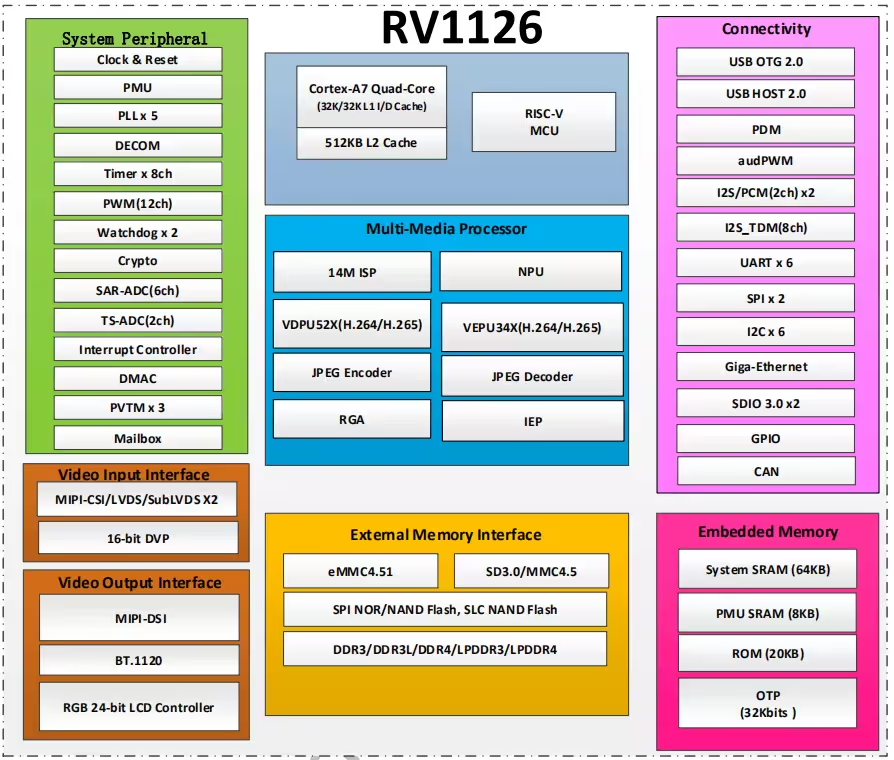

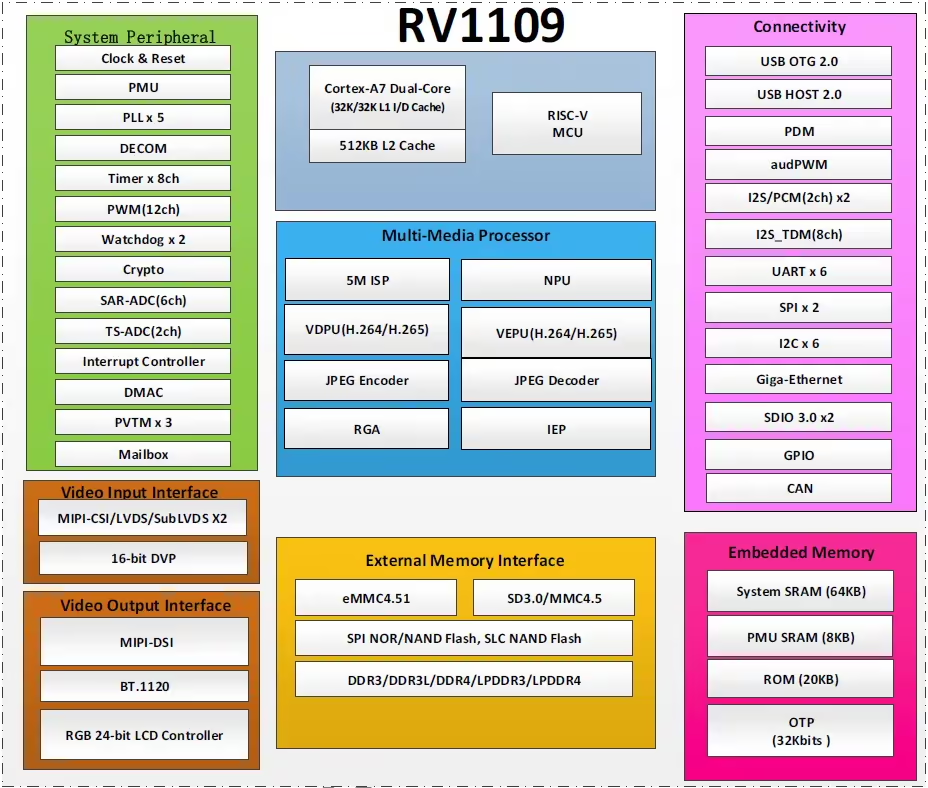

RV1126 ist ein Hochleistungs-Vision-Prozessor-SoC für IPC/CVR, insbesondere für KI-bezogene Anwendungen. Es basiert auf einem Quad-Core ARM Cortex-A7 32-Bit-Kern, der NEON und FPU integriert. Es gibt einen 32-KB-I-Cache und einen 32-KB-D-Cache für jeden Kern sowie einen 512-KB-Unified-L2-Cache. Die eingebaute NPU unterstützt den INT8/INT16-Hybridbetrieb und die Rechenleistung beträgt bis zu 2,0 TOPs. In Ergänzung, mit seiner starken Verträglichkeit, Netzwerkmodelle, die auf einer Reihe von Frameworks wie TensorFlow/MXNet/PyTorch/Caffe basieren, können einfach konvertiert werden.<Br>

RV1126 führt auch eine neue Generation vollständig hardwarebasierter 14-Megapixel-ISP ein (Bildsignalprozessor) und Postprozessor. Es implementiert viele Algorithmusbeschleuniger, die normalerweise in IPC und CVR verwendet werden, wie HDR, 3A funktioniert (AE, VON, AWB), LSC, 3DNR, 2DNR, Schärfung, entnebeln, Fisheye-Korrektur, Gamma-Korrektur, Erkennung von Merkmalspunkten und so weiter. Alle von ihnen sind Echtzeitverarbeitung. Zusammenarbeit mit zwei MIPI CSI (oder LVDS/SubLVDS) und ein DVP (BT.601/BT.656/BT.1120) Schnittstelle, Benutzer können ein System aufbauen, das Videodaten empfängt 3 Kamerasensoren gleichzeitig.

Der in RV1126 eingebettete Video-Encoder unterstützt UHD H.265/H.264-Codierung. Es unterstützt auch Multi-Stream-Codierung, bis zu einem 4Kp30 und einem 1080p30 gleichzeitig. Mit Hilfe dieser Funktion, Das Video von der Kamera kann mit höherer Auflösung codiert und im lokalen Speicher gespeichert und gleichzeitig in ein anderes Video mit niedrigerer Auflösung in den Cloud-Speicher übertragen werden. Der H.264/H.265-Videodecoder im RV1126 unterstützt 4Kp30 für H.264 und H.265.

Zusätzlich zum bisherigen Hochleistungs-Multimediablock, RV1126 enthält auch reichhaltiges Audio, Erinnerung, und andere periphere Schnittstellen wie I2C, SPI, PWM, und so weiter. Diese können Benutzern dabei helfen, dem gesamten System weitere Sensoren oder andere Peripheriegeräte hinzuzufügen, um die Flexibilität und Erweiterbarkeit zu verbessern.

RV1126 verfügt über einen leistungsstarken externen DRAM (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133) in der Lage, anspruchsvolle Speicherbandbreiten zu unterstützen.

1.2 Eigenschaften

Die unten aufgeführten Funktionen, die in einem tatsächlichen Produkt vorhanden sein können oder nicht, können den Lizenzanforderungen von Drittanbietern unterliegen. Bitte kontaktieren Sie Rockchip für aktuelle Produktkonfigurationen und Lizenzanforderungen.

1.2.1 Anwendungsprozessor

Quad-Core-Cortex-A7

Vollständige Implementierung des Befehlssatzes der ARM-Architektur v7-A, ARM Neon Advanced SIMD

Neon und FPU separat integriert

32 KB L1 I-Cache und 32 KB L1 D-Cache pro Cortex-A7-CPU

Einheitlicher 512-KB-L2-Cache für Quad-Core-Cortex-A7

TrustZone-Technologie wird unterstützt

Separate Leistungsdomänen für das CPU-Kernsystem zur Unterstützung des internen Netzschalters und des externen Ein-/Ausschaltens basierend auf dem unterschiedlichen Anwendungsszenario

PD_CPU0: 1st Cortex-A7 + Neon + FPU + L1 I/D-Cache

PD_CPU1: 2nd Cortex-A7 + Neon + FPU + L1 I/D-Cache

PD_CPU2: 3rd Cortex-A7 + Neon + FPU + L1 I/D-Cache

PD_CPU3: 4th Cortex-A7 + Neon + FPU + L1 I/D-Cache

Eine isolierte Spannungsdomäne zur Unterstützung von DVFS

1.2.2 Video-Input-Schnittstelle

Schnittstelle und Videoeingangsprozessor

Zwei MIPI CSI/LVDS/SubLVDS Schnittstellen, 4 Bahnen jeweils, Die maximale MIPI CSI-Datenrate beträgt 2,5 Gbit/s/Spur, Die maximale Datenrate von LVDS/SublVDS beträgt 1 Gbit/s/Spur

Auf 8/10/12/16-Bit-Standard-DVP-Schnittstelle, bis zu 150 MHz Eingangsdaten

Unterstützt BT.601/BT.656 und BT.1120 VI-Schnittstellen

Unterstützen Sie die Polarität von pixel_clk、hsync、vsync konfigurierbar

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

ISP

Die maximale Auflösung beträgt 14 Megapixel(4416×3312)

DVP-Eingang: ITU-R BT.601/656/1120 mit raw8/raw10/raw12/raw16, YUV422

MIPI-Eingang: RX-Datenspur x1/x2/x4, roh8/roh10/roh12, YUV422

3A: einschließlich AE/Histogramm, VON, AWB-Statistikausgabe

FPN: Entfernung von Musterrauschen behoben

BLC: Schwarzwertkorrektur

DPCC: Statische/dynamische Pixelcluster-Korrektur

LSC: Linsenschattierungskorrektur

Bayer-NR: Bayer-rohes Entrauschen, 2DNR

HDR: 3-/2-Frame Merge in High-Dynamic Range

TMO: 3-/2-Frame Merge Video Tone Mapping

WDR: One Frame Wide-Dynamic Range Tone Mapping

Debayer: Erweitertes adaptives Demosaic mit chromatischer Aberrationskorrektur

CCM/CSM: Farbkorrekturmatrix; RGB2YUV usw.

Gamma: Gamma-Out-Korrektur

Dunst entfernen/verbessern: Automatische Dehaze- und Kantenverbesserung

3DLUT: 3D-Lut-Farbpalette für Kunden

LDCH: Linsenverzerrung in horizontaler Richtung

Ausgangsskalierung*3: Unterstützung beim Herunterskalieren der Ebene * 3(W0<3264; W1<1280; W2<1280)

Ausgangsskalierung*2: Unterstützungsskalierung nach unten Ebene * 2(W0<1920; W1<1920)

Ausgabe (FBC): unterstützt YUV422/420 mit Frame Buffer Compression

3DNR: Erweiterte zeitliche Rauschunterdrückung in YUV

2DNR: Erweiterte räumliche Rauschunterdrückung in YUV

Scharf: Bildschärfung &Ampere; Kantenverstärkung in YUV

ORB: Schnell orientiert und gedreht BRIEF, eine Methode zur Erkennung von Merkmalspunkten

FEC: die größere Linsenverzerrung und Fischaugenkorrektur

CGC: Komprimierung des Farbumfangs, YUV-Vollbereichs-/Grenzbereichskonvertierung

1.2.3 Video-Codec

Video-Decoder

Echtzeit-Decodierung von H.264 und H.265

Haupt- und Haupt10-Profil für H.265, bis zum Niveau 5.0 und 4096×2304@30fps

Grundlinie, hauptsächlich, hoch, hoch10 und hoch 4:2:2(ohne MBAFF), bis zum Niveau 5.1 und 4096×2304@30fps

Video-Encoder

UHD H.265/H.264-Videocodierung in Echtzeit

I-/P-Frames und SmartP-Referenz.

Steuermodi mit fünf Bitraten (CBR, VBR, FixQp, AVBR, und QpMap)

Bis zu 100 Mbit/s Ausgangsbitrate

Unterstützen Sie den ROI(keine Begrenzung) Codierung;

Hochkarätig für H.264, bis zum Niveau 5.1 und 4096×2304@30fps

Hauptprofil für H.265, bis zum Niveau 5.0 und 4096×2304@30fps

Unterstützung für Multi-Stream-Codierung

3840 x 2160 bei 30 fps + 1080p@30 fps Codierung

3840 x 2160@30-Codierung + 3840 x 2160 @ 30 fps Dekodierung

Eingabedatenformat:

YCbCr 4:2:0 eben

YCbCr 4:2:0 halbplanar

YCbYCr 4:2:2

CbYCry 4:2:2 verschachtelt

RGB444 und BGR444

RGB555 und BGR555

RGB565 und BGR565

RGB888 und BRG888

RGB101010 und BRG101010

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

Eine isolierte Spannungsdomäne zur Unterstützung von DVFS

1.2.4 JPEG-CODEC

JPEG-Encoder

Grundlinie (DCT sequentiell)

Die Encodergröße reicht von 96×96 bis 8192×8192(67MPixel)

Bis zu 90 Millionen Pixel pro Sekunde

JPEG-Decoder

Die Decodergröße reicht von 48×48 bis 8176×8176(66.8MPixel)

Bis zu 76 Millionen Pixel pro Sekunde

1.2.5 Neuronale Prozesseinheit

Beschleunigungs-Engine für neuronale Netzwerke mit einer Verarbeitungsleistung von bis zu 2.0 SPITZEN

Ganzzahl unterstützen 8, ganze Zahl 16 Faltungsoperation

Deep-Learning-Frameworks unterstützen: TensorFlow, TF-lite, Pytorch, Kaffee, ONNX, MXNet, Schwer, Darknet

Unterstützung der OpenVX-API

Eine isolierte Spannungsdomäne zur Unterstützung von DVFS

1.2.6 Gedächtnisorganisation

Interner On-Chip-Speicher

BootRom

SYSTEM_SRAM im Spannungsbereich von VD_LOGIC

PMU_SRAM im Spannungsbereich von VD_PMU für Low-Power-Anwendungen

Externer Off-Chip-Speicher

DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133①

SPI-Flash

eMMC

SD-Karte

Asynchron und Flash

1.2.7 Interner Speicher

Internes BootRom

Systemstart von folgendem Gerät unterstützen:

FSPI-Flash-Schnittstelle

eMMC-Schnittstelle

SDMMC-Schnittstelle

Asynchrone NAND-Schnittstelle

Unterstützung des Systemcode-Downloads über die folgende Schnittstelle:

USB-OTG-Schnittstelle (Gerätemodus)

SYSTEM_SRAM

Größe: 64KB

PMU_SRAM

Größe: 8KB

1.2.8 Externer Speicher oder Speichergerät

Dynamische Speicherschnittstelle (DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133)

Kompatibel mit JEDEC-Standards

Kompatibel mit DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133

Unterstützt 32-Bit-Datenbreite, 2 Reihen (Chip wählt), max. 4 GB Adressraum pro Rang, Der gesamte Adressraum beträgt 4 GB (max)

Energiesparmodi, wie Power-Down und Self-Refresh für SDRAM

eMMC-Schnittstelle

Kompatibel mit Standard-iNAND-Schnittstelle

Kompatibel mit der eMMC-Spezifikation 4.51

Unterstützt drei Datenbusbreiten: 1-Bit, 4-Bit oder 8 Bit

Unterstützung bis HS200; unterstützt aber keine CMD-Warteschlange

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

SD/MMC-Schnittstelle

Kompatibel mit SD3.0, MMC-Version 4.51

Die Datenbusbreite beträgt 4 Bit

Flexible serielle Flash-Schnittstelle(FSPI)

Unterstützt die Datenübertragung von/zu einem seriellen Flash-Gerät

Unterstützung x1, x2, x4-Datenbit-Modus

Unterstützung 2 Chips auswählen

NAND-Flash-Schnittstelle

Unterstützt Async und Flash

Die Datenbusbreite beträgt 8 Bit

Unterstützung 1 Chip auswählen

Unterstützt LBA und Flash

Bis zu 16 Bit/1 KB Hardware-ECC

Unterstützt konfigurierbares Schnittstellen-Timing

1.2.9 Systemkomponente

RISC-V-MCU

32bit Mikrocontrollerkern mit RISC -V ISA

Harvard-Architektur, separate Anweisung, und Datenspeicher

Der Befehlssatz ist RV32I mit M- und C-Erweiterungen

Integrierter programmierbarer Interrupt-Controller (IPIC), alle 123 IRQ-Leitungen, die mit GIC für Cortex-A7 verbunden sind, werden auch mit RISC –V MCU verbunden

Integrierter Debug-Controller mit JTAG-Schnittstelle

CRU (Uhr &Ampere; Einheit zurücksetzen)

Unterstützung der Clock-Gating-Steuerung für einzelne Komponenten

Ein Oszillator mit 24 MHz Takteingang

Unterstützt globale Soft-Reset-Steuerung für den gesamten Chip, auch individueller Soft-Reset für jede Komponente

PMU (Power-Management-Einheit)

Unterstützung 5 separate Spannungsdomänen VD_CORE/VD_LOGIC/VD_PMU/VD_NPU/VD_VEPU

Unterstützung 14 getrennte Machtbereiche, die per Software basierend auf verschiedenen Anwendungsszenen ein- und ausgeschaltet werden können

Mehrere konfigurierbare Arbeitsmodi zum Energiesparen durch unterschiedliche Frequenzen oder automatische Clock-Gating-Steuerung oder Power Domain On/Off-Steuerung

Timer

Unterstützung 6 64Bit-Timer mit dem Interrupt-basierten Betrieb für unsichere Anwendungen

Unterstützung 2 64Bit-Timer mit Interrupt-basiertem Betrieb für sicheren Einsatz

Unterstützt zwei Betriebsmodi: freilaufende und benutzerdefinierte Zählung

Support-Timer-Arbeitszustand überprüfbar

PWM

Unterstützung 12 On-Chip-PWMs (PWM0 ~ PWM11) mit dem Interrupt-basierten Betrieb

Der programmierbare vorskalierte Betrieb zum Bustakt und dann weiter skaliert

Eingebettete 32-Bit-Zeitgeber-/Zählerfunktion

Aufnahmemodus unterstützen

Unterstützt kontinuierlichen Modus oder One-Shot-Modus

Bietet Referenzmodus und gibt verschiedene Arbeitszyklus-Wellenformen aus

Optimiert für IR-Anwendung für PWM3, PWM7, und PWM11

Wachhund

32-Bit-Watchdog-Zähler

Der Zähler zählt von einem voreingestellten Wert bis herunter 0 um das Auftreten einer Zeitüberschreitung anzuzeigen

WDT kann zwei Arten von Operationen ausführen, wenn das Timeout auftritt:

Erzeugen Sie einen System-Reset

Zuerst, einen Interrupt erzeugen und wenn dieser nicht von der Serviceroutine gelöscht wird, bis ein zweiter Timeout auftritt, dann einen System-Reset erzeugen

Programmierbare Reset-Impulslänge

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

Absolut 16 definierte Bereiche der Haupt-Timeout-Periode

Ein Watchdog für unsichere Anwendungen

Ein Watchdog für sichere Anwendung

Interrupt-Controller

Unterstützung 128 SPI-Interrupt-Quelleneingang von verschiedenen Komponenten

Unterstützung 16 softwaregetriggerte Interrupts

Zwei Interrupt-Ausgänge (nFIQ und nIRQ) separat für jeden Cortex-A7, beide sind niedrigpegelempfindlich

Unterstützen Sie unterschiedliche Interrupt-Prioritäten für jede Interrupt-Quelle, und sie sind immer softwareprogrammierbar

DMAC

DMA auf Basis der Mikrocode-Programmierung

Die DMA-Funktion für verkettete Listen wird unterstützt, um die Scatter-Gather-Übertragung abzuschließen

Unterstützt Datenübertragungsarten mit Memory-to-Memory, Speicher-zu-Peripherie, Peripherie-zu-Speicher

Signalisiert das Auftreten verschiedener DMA-Ereignisse unter Verwendung der Interrupt-Ausgangssignale

Ein eingebetteter DMA-Controller für das System

DMAC-Funktionen:

Unterstützung 8 Kanäle

27 Hardwareanforderungen von Peripheriegeräten

2 unterbricht die Ausgabe

Unterstützung der TrustZone-Technologie und des programmierbaren sicheren Zustands für jeden DMA-Kanal

Sicheres System

Cipher-Engine

Unterstützt SM2/SM3/SM4-Verschlüsselung

Unterstützung von SHA-1, SHA-256/224, SHA-512/384, und MD5 mit Hardwarepolsterung

Element der Support-Link-Liste (LLI) DMA-Übertragung

Unterstützt AES-128 AES-256-Verschlüsselung &Ampere; Chiffre entschlüsseln

Unterstützt den AES ECB/CBC/OFB/CFB/CTR/CTS/XTS-Modus

DES-Unterstützung &Ampere; TDES verschlüsseln &Ampere; Chiffre entschlüsseln

Unterstützung des DES/TDES ECB/CBC/OFB/CFB-Modus

Unterstützung bis zu 4096 Bits PKA mathematische Operationen für RSA/ECC

Unterstützt bis zu 8-Kanal-Konfiguration

Unterstützung bis zu 256 Bits der TRNG-Ausgabe

Unterstützung von Datenverschlüsselung für alle DDR-Typen

Unterstützt sicheres OTP

Unterstützt sicheres Debuggen

Unterstützt ein sicheres Betriebssystem

Postfach

Eine Mailbox im SoC für die A7- und RISC-V-MCU-Kommunikation

Unterstützt vier Mailbox-Elemente pro Mailbox, jedes Element enthält ein Datenwort, ein Befehlswortregister, und ein Flag-Bit, das eine Unterbrechung darstellen kann

Bereitstellen 32 Sperrregister für Software zur Verwendung, um anzuzeigen, ob die Mailbox besetzt ist

KINDER

Unterstützung für das Dekomprimieren von GZIP-Dateien

Unterstützung für das Dekomprimieren von LZ4-Dateien, einschließlich der allgemeinen Struktur des LZ4-Frame-Formats und des Legacy-Frame-Formats.

Unterstützung für das Dekomprimieren von Daten im Deflate-Format

Unterstützung für die Dekomprimierung von Daten im ZLIB-Format

Unterstützung vollständiger Interrupt- und Fehler-Interrupt-Ausgaben

Unterstützung der Hash32-Prüfung im LZ4-Dekomprimierungsprozess

Unterstützen Sie die Größenbegrenzungsfunktion der dekomprimierten Daten, um zu verhindern, dass der Speicher während des Dekomprimierungsprozesses böswillig zerstört wird

Unterstützungssoftware zum Stoppen des Dekomprimierungsprozesses

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

1.2.10 Grafik-Engine

2D-Grafik-Engine (RGA):

Quellformate:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planar, YUV420 halbplanar

YUV422 planar, YUV422 halbplanar

YUV 10 Bit für YUV420/422 halbplanar

BPP8, BPP4, BPP2, BPP1

Zielformate:

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planar, YUV420 halbplanar

YUV422 planar, YUV422 halbplanar

Konvertierung des Pixelformats, BT.601/BT.709

Maximale Auflösung: 8192×8192-Quelle, 4096×4096 Ziel

BitBlt

Zwei Quellen BitBLT:

A+B=B nur BitBLT, A unterstützt drehen und skalieren, wenn B fixiert ist

A+B=C zweite Quelle (B) hat das gleiche Attribut wie (C) plus Rotationsfunktion

Farbfüllung mit Verlaufsfüllung, und Musterfüllung

Leistungsstarkes Dehnen und Schrumpfen

Monochrome Erweiterung für die Textwiedergabe

Neues umfassendes Alpha pro Pixel (Farb-/Alphakanal getrennt)

Alpha-Mischmodi einschließlich Java 2 Porter-Duff-Compositing-Mischregeln, Chroma-Schlüssel, Mustermaske, Fading

Dither-Betrieb

0, 90, 180, 270-Grad Drehung

x-Spiegel, y-Spiegel, und Rotationsbetrieb

Bildverbesserungsprozessor (IEP):

Bildformat

Daten eingeben: YUV420 / YUV422, halbplanar/planar, UV-Tausch

Daten ausgeben: YUV420 / YUV422, halbplanar, UV-Tausch, Kachelmodus

YUV-Downsampling-Konvertierung von 422 nach 420

Maximale Auflösung für dynamische Bilder bis zu 1920×1080

Deinterlace

1.2.11 Anzeigeschnittstelle

Ein bis zu 24 bits RGB parallele Videoausgangsschnittstelle

Eine BT.1120-Videoausgangsschnittstelle

Eine 4-spurige MIPI-DSI-Schnittstelle, bis zu 1 Gbit/s pro Spur

Bis zu 1080p@60fps

1.2.12 Videoausgabeprozessor (AGB)

Bis zu 1920×1080 @60fps

Mehrlagig

Hintergrundebene

Win0-Schicht

Win2-Schicht

Eingabeformat: RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444

1/8 nach 8 Scale-down- und Scale-up-Engine

Unterstützt virtuelle Anzeige

256 Level-Alpha-Blending (vormultiplizierte Alpha-Unterstützung)

Transparenz-Farbschlüssel

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

RGB2YCbCr (BT.601/BT.709)

Unterstützung mehrerer Regionen

Win0-Layer und Win2-Layer-Overlay austauschbar

Unterstützung von RGB- oder YUV-Domain-Overlay

BCSH (Helligkeit, Kontrast, Sättigung, Farbtonanpassung)

BCSH: YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

BCSH: RGB2YCbCr (BT.601/BT.709)

Unterstützung der Gamma-Anpassung

Unterstützt Dithering nach unten allegro RGB888to666 RGB888to565 &Ampere; Dithering nach unten FRC (konfigurierbar) RGB888 bis 666

Leeres und schwarzes Display

1.2.13 Audio-Interface

I2S0 mit 8 Kanäle

Bis zu 8 Kanäle TX und 8 Kanäle RX-Pfad

Audioauflösung von 16 Bit bis 32 Bit

Abtastrate bis zu 192 kHz

Bietet Master- und Slave-Arbeitsmodus, Software konfigurierbar

Unterstützung 3 I2S-Formate (normal, linksbündig, rechtsbündig)

Unterstützung 4 PCM-Formate (frühzeitig, spät1, spät2, spät3)

I2S- und PCM-Modus können nicht gleichzeitig verwendet werden

I2S1/I2S2 mit 2 Kanäle

Bis zu 2 Kanäle für TX u 2 Kanäle RX-Pfad

Audioauflösung von 16 Bit bis 32 Bit

Abtastrate bis zu 192 kHz

Bietet Master- und Slave-Arbeitsmodus, Software konfigurierbar

Unterstützung 3 I2S-Formate (normal, linksbündig, rechtsbündig)

Unterstützung 4 PCM-Formate (frühzeitig, spät1, spät2, spät3)

I2S und PCM können nicht gleichzeitig verwendet werden

PDM

Bis zu 8 Kanäle

Audioauflösung von 16 Bit bis 24 Bit

Abtastrate bis zu 192 kHz

Unterstützung des PDM-Master-Empfangsmodus

TDM

Unterstützung bis zu 8 Kanäle für TX u 8 Kanäle für den RX-Pfad

Audioauflösung von 16 Bit bis 32 Bit

Abtastrate bis zu 192 kHz

Bietet Master- und Slave-Arbeitsmodus, Software konfigurierbar

Unterstützung 3 I2S-Formate (normal, linksbündig, rechtsbündig)

Unterstützung 4 PCM-Formate (frühzeitig, spät1, spät2, spät3)

Audio-PWM

Unterstützt die Konvertierung von PCM in das PWM-Format

Abtastrate bis zu 16x

Unterstützt lineare Interpolation für 2x/4x/8x/16 Oversampling

Unterstützung 8/9/10/11 Bits maskierbarer L/R-Kanal-PWM-Ausgang

Digitaler Audio-Codec

Unterstützt 3-Kanal-Digital-ADC

Unterstützt 2-Kanal-Digital-DAC

Unterstützung der I2S/PCM-Schnittstelle

Unterstützung des I2S/PCM-Master- und Slave-Modus

Unterstützt 4-Kanal-Audioübertragung im I2S-Modus

Unterstützt 2-Kanal-Audioempfang im I2S-Modus

Unterstützt 2-Kanal-Audioübertragung oder -empfang im PCM-Modus

Unterstützt eine Abtastauflösung von 16 bis 24 Bit für digitalen ADC und digitalen DAC

<Span-Stil =“Farbe: #fffff;“>RV1126 Datenblatt Rev. 1.4</Spanne>

Sowohl der digitale ADC als auch der digitale DAC unterstützen drei Gruppen von Abtastraten. Gruppe 0 sind 8kHz/16kHz/32kHz/64kHz/128kHz, Gruppe 1 sind 11,025 kHz/22,05 kHz/44,1 kHz/88,2 kHz/176,4 kHz und Gruppe 2 sind 12kHz/24kHz/48kHz/96kHz/192kHz

Der Durchlassbereich digitaler ADC-Filter beträgt 0,45625*fs

Unterstützung der digitalen ADC-Durchlassbandwelligkeit innerhalb von +/-0,1 dB

Das Sperrband digitaler ADC-Filter beträgt 0,5*fs

Unterstützt eine digitale ADC-Sperrbanddämpfung von mindestens 60 dB

Unterstützung der Lautstärkeregelung für digitalen ADC und digitalen DAC

Unterstützung der automatischen Pegelregelung (ALC)und Noise Gate für digitalen ADC

Unterstützt die Kommunikation mit Analog Codec über den I2C-Bus

1.2.14 Connectivity

SDIO-Schnittstelle

Kompatibel mit SDIO3.0-Protokoll

4 Bit Datenbusbreite

GMAC 10/100/1000M Ethernet-Controller

Unterstützt Datenübertragungsraten von 10/100/1000 Mbit/s mit den RGMII-Schnittstellen

Unterstützt Datenübertragungsraten von 10/100 Mbit/s mit den RMII-Schnittstellen

Unterstützt sowohl Vollduplex- als auch Halbduplex-Betrieb. Unterstützung für TCP Segmentation Offload (ÜNB) und UDP-Segmentierungsauslagerung (VERWENDEN) Netzwerkbeschleunigung<Br>

USB 2.0 Wirt

Kompatibel mit USB 2.0 Spezifikation

Unterstützt Hochgeschwindigkeit(480Mbps), Vollgas(12Mbps) und langsam(1.5Mbps) Modus

Unterstützt erweiterte Host-Controller-Schnittstellenspezifikation (EHCI), Revision 1.0

Unterstützt Open Host Controller Interface Specification (OHCI), Revision 1.0a

USB 2.0 OTG

Kompatible Spezifikation

Universal Serial Bus-Spezifikation, Revision 2.0

Erweiterbare Host-Controller-Schnittstelle für Universal Serial Bus (xHCI), Revision 1.1

Unterstützung von Steuerung/Bulk/Interrupt/Isochronous Transfer

SPI-Schnittstelle

Unterstützung 2 SPI-Controller, unterstützt zwei Chip-Select-Ausgänge

Unterstützt Serial-Master- und Serial-Slave-Modus, Software-konfigurierbar

I2C-Schnittstelle

Unterstützung 6 I2C-Schnittstellen(I2C0-I2C5)

Unterstützt 7-Bit- und 10-Bit-Adressmodus

Softwareprogrammierbare Taktfrequenz

Daten auf dem I2C-Bus können im Standardmodus mit Raten von bis zu 100 kbit/s übertragen werden, bis zu 400 kBit/s im Fast-Modus, oder bis zu 1 Mio. Bit/s im Fast-Modus Plus

UART-Schnittstelle

Unterstützung 6 UART-Schnittstellen (UART0-UART5)

Unterstützt 5bit, 6Bit, 7Bit, und serielle 8-Bit-Daten senden oder empfangen

Standardasynchrone Kommunikationsbits wie Start, Pause, und Parität

Unterstützt verschiedene Eingangstakte für den UART-Betrieb, um eine Baudrate von bis zu 4 MBit/s zu erreichen

Unterstützt den automatischen Flusssteuerungsmodus(außer UART2)

1.2.15 Andere

Mehrere Gruppen von GPIO

Alle GPIOs können verwendet werden, um einen Interrupt zu erzeugen

Support-Level-Trigger und Flanken-Trigger-Interrupt

Unterstützt konfigurierbare Polarität des Level-Trigger-Interrupts

Unterstützt konfigurierbare steigende Flanke, fallende Flanke, und beide Flanken lösen Interrupt aus

Konfigurierbare Zugrichtung unterstützen (ein schwacher Pull-up und ein schwacher Pull-down)

<stark>RV1126 Datenblatt Rev. 1.4</stark>

Unterstützt konfigurierbare Antriebsstärke

Temperatursensor (TS-ADC)

Unterstützt den benutzerdefinierten Modus und den automatischen Modus

Im benutzerdefinierten Modus, start_of_conversion kann vollständig per Software gesteuert werden, und können auch durch Hardware erzeugt werden.

Im Automatikmodus, die Alarmtemperatur(hohe/niedrige Temperatur) Interrupt kann konfigurierbar sein

Im Automatikmodus, Die Temperatur des System-Resets kann konfigurierbar sein

Unterstützung für 2 Kanal TS-ADC (verwendet für CPU bzw. NPU), Die Temperaturkriterien jedes Kanals können konfiguriert werden

-40~125°C Temperaturbereich und 5°C Temperaturauflösung

12-Bit-SAR-ADC bis zu 732 S/s-Abtastrate

ADC mit sukzessiver Annäherung (SAR-ADC)

10-Bit-Auflösung

Bis zu 1 MS/s Abtastrate

6 single-ended Eingangskanäle

OTP

Unterstützung von 32-Kbit-Speicherplatz und höherem 4-KByte-Adressraum ist ein nicht sicherer Teil.

Unterstützt das Lesen und Programmieren von Wortmasken in einem sicheren Modell

Stützprogrammlänge von 1 nach 32 Bit

Lesevorgang unterstützt nur 8 Bit

Programm- und Lesestatus können gelesen werden

Das Programm kann den Datensatz nicht adressieren

Pakettyp

FCCSP 409-Pin (Karosserie: 14mm x 14 mm; Kugelgröße: 0.3Millimeter; Ballplatz: 0.65Millimeter)

Anmerkungen:

①: DDR3/DDR3L/DDR4/LPDDR3/LPDDR4 wird nicht gleichzeitig verwendet

Herunterladen

RKDevTool_Release_v2.74

https://drive.google.com/file/d/19rfUc4DJP5bPmdeCoDLsawo9b8zZxKMH/view?usp=sharing

SDK

https://drive.google.com/file/d/1CCNWHNNVi8FVG6UXNgrMDYsZx3SrpFyr/view?usp=sharing

Datenblatt

RV1126 RV1109 Schnellstart

Rockchip_RV1126_RV1109_Quick_Start_Linux_EN

Rockchip-Entwicklerhandbuch RockX_SDK

Anpassung des RV1126-Entwicklungsboards

W-LAN & Bluetooth

Eine weitere Markenkamera als Ersatz für Sony IMX415

Ein USB-Kameraeingang, Überträgt das Video-Streaming per WLAN-Modul auf einen anderen Computer

Rezensionen

Es gibt noch keine Rezensionen.